请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

主题中讨论的其他器件:TMS570LC4357在 Windows 下使用 CCS 10.4.0.00006检查 Cortex-R5运算是否存在浮点除法为零时、希望使用反汇编视图确认编译器已发出浮点除法指令。

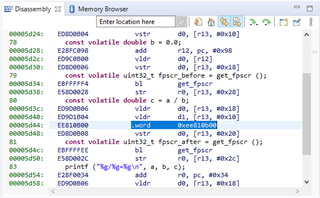

注意到 CCS Disassembly 视图显示".word 0xee810b00"、因此无法识别指令:

Cortex-R5处于 ARM 模式、将"Mixed ARM/Thumb"更改为"ARM Only"并不会产生什么不同。

通过查看编译器保存的汇编器列表、可以看到编码 为 EE810B00的预期 VDIV.F64指令:

170 .dwpsn file "../source/HL_sys_main.c",line 80,column 29,is_stmt,isa 2

171 00000030 ED9D0B06 VLDR.64 D0, [SP, #24] ; [DPU_V7R4_PIPE0] |80|

172 00000034 ED9D1B04 VLDR.64 D1, [SP, #16] ; [DPU_V7R4_PIPE0] |80|

173 00000038 EE810B00 VDIV.F64 D0, D1, D0 ; [DPU_V7R4_PIPE0] |80|

174 0000003c ED8D0B08 VSTR.64 D0, [SP, #32] ; [DPU_V7R4_PIPE0] |80|

所使用的工程已附加。