Other Parts Discussed in Thread: ADC09SJ1300

主题ADC09SJ1300中讨论的其他器件

工具与软件:

您好、专家。

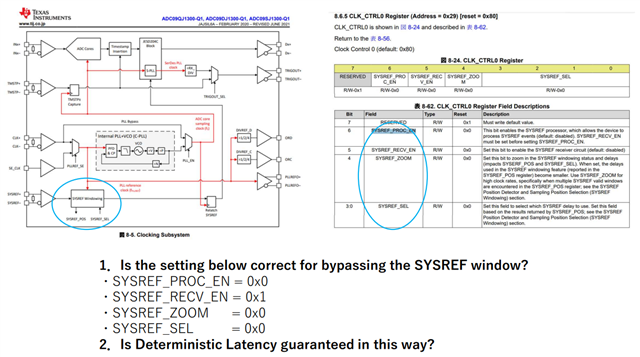

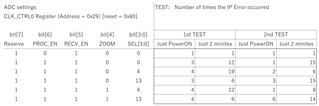

在我们的电路板上、SYSREF 窗口不是很有效、并且 TI-JESD204C-IP 的"无效/NotInTable/F差别化"错误的频率很高。

我想使用 SYSREF 信号本身、但考虑不使用 SYSREF 窗口。

请告诉我两件事。

绕过 SYSREF 窗口时、以下设置是否正确?

-

SYSREF_PROC_EN=0x0

-

SYSREF_RECV_EN=0x1

-

SYSREF_ZOOM = 0x0

-

SYSREF_SEL=0x0

2. 是否以这种方式保证了确定性延迟?

谢谢你。