工具/软件:

您好、

我使用的是 ADS5560、我担心在采用交流耦合的单端模式下运行(CLKM 通过0.1 µF 电容器接地)时的输入时钟信号。

问题:

-

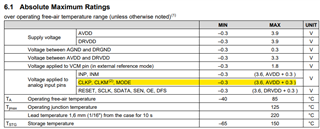

根据数据表、CLKP 的绝对最小电压为-0.3V。

-

由于我的时钟信号是交流耦合的、因此它以0V 为中心、这意味着它不可避免地超过-0.3V 限值。

-

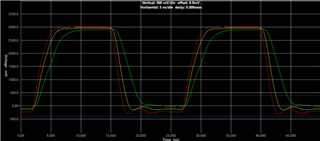

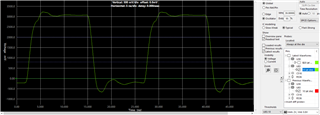

我使用 HyperLynx 模拟了接收到的信号、看起来像这样:

可以看到、它超过了-0.3V 的限值。

分析:

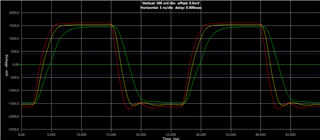

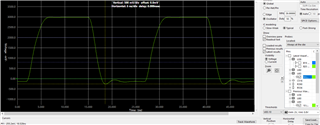

我假设-0.3V 限值是由于 VCM = 1.5V 的内部5kΩ 上拉电阻造成的。 因此、我重复了仿真、现在包括该上拉电阻的影响:

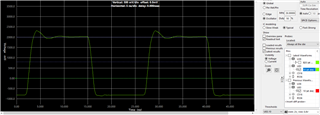

正如预期的那样、信号现在以1.5V 为中心、但仍超出了-0.3V 限制。 为了使信号保持在指定范围内、我发现需要一个最小串联电阻250Ω:

但是、添加这样的大串联电阻会降低压摆率、进而增加抖动、可能影响 ADC 性能。

问题:

-

CLKP 的-0.3V 限制有多严格? 鉴于交流耦合本身会导致电压偏移超过该限值、该规格是否意味着是绝对限制?

-

是否有一种对时钟信号进行交流耦合、同时保持在电压限值范围内而不降低压摆率的建议方法?

-

关于数据表的图53、我按照建议测试了将 VCM 与 CLKM 的连接和断开连接、但我发现几乎没有差别(因为 CLKM 已经有一个连接到 VCM 的内部5kΩ 上拉电阻)。 将 VCM 从外部连接到 CLKM 是否有任何实际好处?

任何见解都将非常感谢。

谢谢!