主题ADC14X250中讨论的其他器件

工具/软件:

您好、

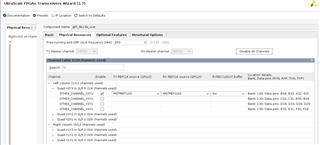

我的工程将 ZCU102与 ADC14X250 EVM 相连。 配置 IP 以匹配 ADC 功能(8b10b、1个 Rx 通道、5Gbps 通道速率等)后、下一步是开发应用层。 为此、计划在仿真中连接 TI-JESD204 IP 的 Tx 和 Rx 端与应用逻辑。

但是、在运行 TI-JESD204 IP Questa 仿真模型时遇到问题。 但是、cpll 和 qpll 输出始终保持高阻抗("Z")。 我尝试将 Xilinx GTH 收发器的仿真库添加到我的 Questa 环境中、但这也没有用。

有关仿真设置的一些信息:

- mgt_freerun_clk 在100MHz 上运行

- mgt_refclk_p/n 在156.25MHz 上运行(与 zcu102 8b10b 参考设计相同)

-两个系统时钟都以156.25MHz 运行(与 zcu102 8b10b 参考设计相同)

- MASTER_RESET_n 保持低电平达200ns、然后保持高电平

-模拟运行时间200us

此 QuestaSim 模拟工作流是否完全受支持、或者是否存在限制?

谢谢

--

Mariano Mate