Thread 中讨论的其他器件:ADS127L18

工具/软件:

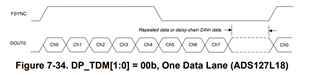

单通道在所有测试的采样率32Ksps - 512Ksps 下运行良好、但我们尚未找到一种方法将 ADS127L18配置为在64Ksps 的时间多路复用模式下使用两个通道、即仅使用 D0数据通道。

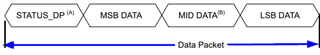

预期是从通道0和1获取样本、以便当通道0中没有信号时、每隔一个采样值接近零、并且状态字节承载通道编号0、1、1、……

配置时、您能在其中找到错误吗?

-----

RetVal |= ratSpiWriteAds127Reg (GEN_CFG1、0); //默认值

RetVal || ratSpiWriteAds127Reg (GEN_CFG2、0b00000110);// fclk 32.768Hz、而不是内部25.6MHz

RetVal |= ratSpiWriteAds127Reg (GEN_CFG3、0b10000000);// SAI 中的完整输出压摆率、注释掉默认值较慢的压摆率

// DP_CFG1德州仪器(TI)建议0b01110000、位5-4的差异意味着8个数据通道

RetVal || ratSpiWriteAds127Reg (DP_CFG1、 0b0100000);//启用数据端口状态字节、一个数据通道

// DP_CFG2模式取决于模式

// CLK_CFG 取决于 MODE

// GPIO 寄存器处于默认值(低禁用输出)

// CHn_CFG1默认值(正常极性、正常范围、缓冲器已禁用)

// CH0_CFG2和 CHN1_CFG2为模式(取决于模式)

RetVal || ratSpiWriteAds127Reg (CH2_CFG2、0b00100000);//断电

RetVal || ratSpiWriteAds127Reg (CH3_CFG2、0b00100000);//断电

RetVal || ratSpiWriteAds127Reg (CH4_CFG2、0b00100000);//断电

RetVal || ratSpiWriteAds127Reg (CH5_CFG2、0b00100000);//断电

RetVal || ratSpiWriteAds127Reg (CH6_CFG2、0b00100000);//断电

RetVal || ratSpiWriteAds127Reg (CH7_CFG2、0b00100000);//断电

// CHn 偏移和默认值为0偏移1.0增益的增益

开关(sampleRate){

用例512:// 512Ksps、一个通道

RetVal || ratSpiWriteAds127Reg (DP_CFG2、 0b00000000);// DCLK 为32.768

retval |= ratSpiWriteAds127Reg (CLK_CFG、 0b00001000);//外部时钟、1分频

RetVal |= ratSpiWriteAds127Reg (CH0_CFG2、0b00000000);// OSR32

RetVal || ratSpiWriteAds127Reg (CH1_CFG2、0b00100000);//断电、仅使用 CHN0

休息;

案例64:// 64Kbps、两个通道

RetVal || ratSpiWriteAds127Reg (DP_CFG2、 0b00000000);// DCLK 为32.768

retval |= ratSpiWriteAds127Reg (CLK_CFG、 0b00001011);//外部时钟、4分频

RetVal || ratSpiWriteAds127Reg (CH0_CFG2、0b00000001);// OSR64

RetVal || ratSpiWriteAds127Reg (CH1_CFG2、0b00000001);// OSR64

休息;