工具/软件:

您好团队:

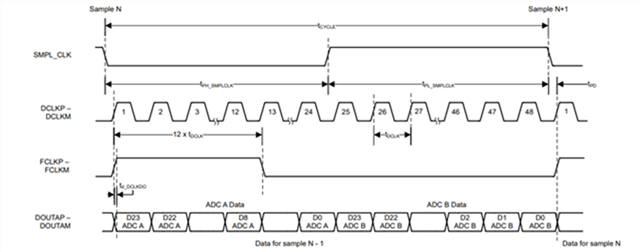

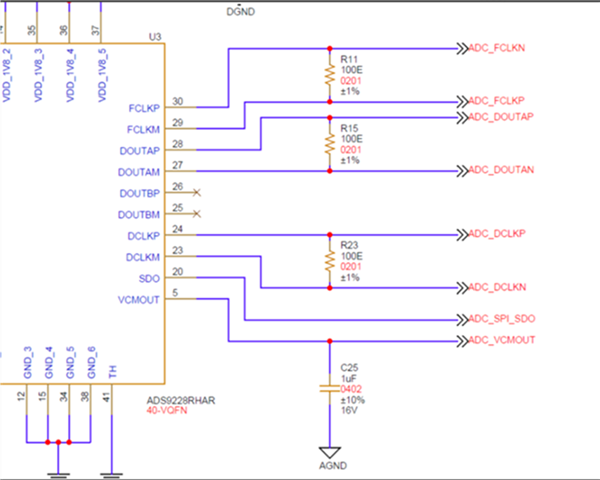

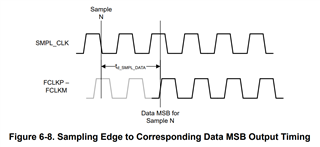

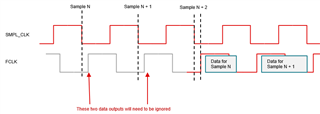

我在工程中使用了 ADS9228RHAR。 我来解释一下、数据是否与尊重的时钟相匹配? 如果是、需要考虑哪个时钟? 请参阅数据表第12页。 我在这里添加了图像以供您参考。

从 ADC 到 FPGA 100E 阻抗已连接。 请参阅原理图。 因此、 数据信号为粉色、 SMPL_CLK 时钟为黄色、FCLK 为橙色。 迄今为止、数据与 SMPL_CLK 匹配。 是正确的、还是我需要相对于 SMPL_CLK 匹配 FCLK。 有人能解释吗?

使用 ADC 独立的模拟和数字接地。