工具/软件:

尊敬的先生/女士:

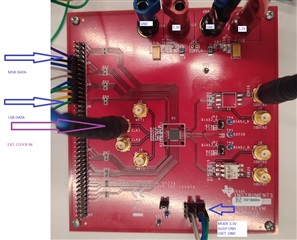

我在设置 DAC5256AEVM 时遇到问题。 我已在下面共享了我的设置的状态信息:

- I SET Mode High 和 SLEEP - GSET 连接到 GND 引脚

-我从 FPGA 生成了 DAC5256AEVM 将使用的数据和时钟。

-我从时钟支持引脚生成了10MHz 时钟信号,并将其提供给 J5 WRT1 SMA 输入。 我提供了与 SMA 引脚的连接。

-我将10MHz 时钟(带有 FPGA)生成的1MHz 正弦信号的正弦连接到 DA 引脚,余弦连接到 DB 引脚到数据引脚。 我通过跳线提供了这些连接。

-我发送新的数据到评估板下降沿的 FPGA 外部时钟。

-我分享了 FPGA 和 EVM 之间的接地。 我还正确连接了电源电压。

-我们尝试使用平衡-非平衡变压器,但当我们无法获得结果时,我们移除了 IOUTA1/2处的平衡-非平衡变压器并对硬件进行了更改,使 R2、R28、R7 = 0r、R3 = DNP

-其他我使用 ZedBoard 作为 FPGA

尽管这样、我无法在 IOUTA/B 上获得任何输出信号 我的问题到底在哪里?

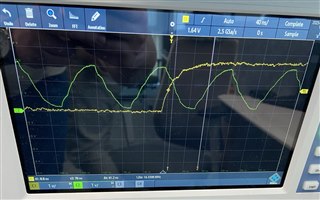

**绿线:FPGA 外部时钟、黄线:数据 MSB 输入

**绿线:FPGA 外部时钟、黄线:数据 MSB 输入