请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC12DL2500 工具/软件:

大家好!

我们正在使用 LMX2582RHAT 我们也看到了一些改进 以及 PCB 布局技术 SPI 信号(CLK、CS、SDI)上的电压。 这些信号由 FPGA 驱动。

以下是当前驱动强度设置:

- SPI_CS#_ADC:12mA

- SPI_CLK_ADC:12 mA

- SPI_MOSI_ADC:12 mA

我们想知道:

- 该过冲和下冲是否在可接受的限值内?

- 如果没有、您可以建议如何减少这些损耗

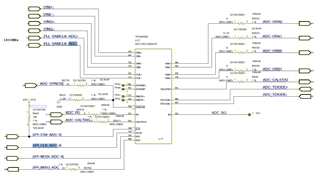

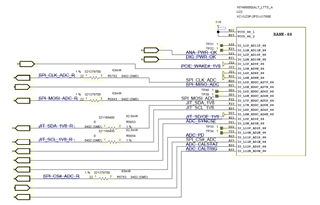

我附上了 SPI 时钟的信号捕获图和相关原理图以供参考。