Other Parts Discussed in Thread: ADS8568

工具/软件:

你(们)好

是否有人能够通过 SPI ATMEGA2560 连接至 ADS8568?

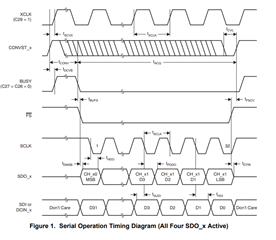

在我当前的应用中、ADS8568 的布局适合串行模式操作。

到目前为止、我未能在 MISO 线上读回读数。

查看 ADS8568 的规格表后、其时序要求似乎比 ATMEGA2560 的要求高得多。

(好像是为了与 C2000 或 FPGA 配合使用)

例如:

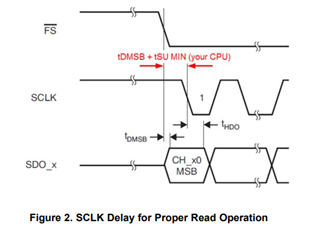

应注意确保的延迟时间

在应用串行时钟之前、满足来自 DMCS/CS 下降沿的最高有效位 (FS)。 减少

延迟指定为最大 12ns

由于 ATMEGA 的工作频率为 16MHz,其最快的指令将在 62nS!

我是否认为 ATMEGA2560 无法通过 SPI 与 ADS8568 通信?

如有任何帮助、我们将不胜感激。