主题: DAC8775 中讨论的其他器件

工具/软件:

您好、

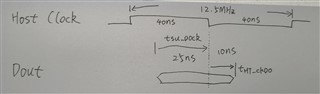

根据 ADS8684 数据表、在最坏情况下、有效的 SDO 宽度为 THT_CKDO + Tsu_Dock = 10ns + 25ns = 35ns。

我知道、随着 SCLK 的频率降低、有效 SDO 宽度将增加。

是否可以像 DAC8775 数据表那样提供从 SCLK 上升沿到 SDO 有效的时间?

谢谢、此致。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

根据 ADS8684 数据表、在最坏情况下、有效的 SDO 宽度为 THT_CKDO + Tsu_Dock = 10ns + 25ns = 35ns。

我知道、随着 SCLK 的频率降低、有效 SDO 宽度将增加。

是否可以像 DAC8775 数据表那样提供从 SCLK 上升沿到 SDO 有效的时间?

谢谢、此致。

感谢您的回答。

根据您绘制的时序图、我的理解是否正确:即使 SCLK 的频率降低、在最坏的情况下、有效的 SDO 宽度仍然是 35ns?

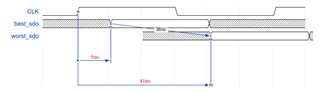

如图所示、当 SCLK 频率降低到 12.5MHz 时、最坏情况下的有效 SDO 宽度为 35ns。

或者、更极端的是、当 SCLK 频率降低到 1MHz 时、最坏情况下的有效 SDO 宽度为 35ns。

换句话说、有效 SDO 宽度与 SCLK 频率无关。

您能否提供降低 CLK 频率与增加 SDO?的设置时间之间的具体定量关系

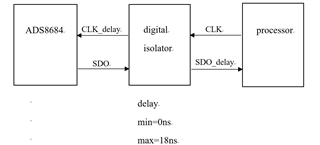

在此应用中:

数字隔离器会导致从输入到输出的信号延迟、最大延迟为 18ns、最小延迟为 0ns。

CLK 周期设置为 60ns(50%占空比)。

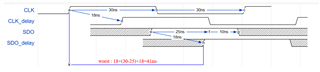

最坏情况下的波形为:

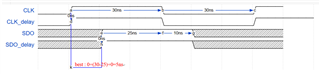

理想情况下的波形为:

在理想情况下和最坏情况下将波形组合在一起是:

图中的时间间隔 (b->c) 为 41-5=36ns >35ns。

在理想情况下和最坏情况下的有效 SDO 之间没有重叠、无论选择采样时如何、都会带来风险。

如果我将 CLK 周期设置为 80ns、建立时间是否可以增加 10ns?

在这种情况下、时间间隔 (b->c) 为 41-5=36ns < 45ns、处理器的采样时间可以为 9ns。

如果我将 CLK 周期设置为 100ns、设置时间是否可以增加 20ns?

在这种情况下、时间间隔 (b->c) 为 41-5=36ns < 55ns、处理器的采样时间可以为 19ns。