请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC12DJ5200RFEVM Thread 中讨论的其他器件:ADC12DJ5200RF

工具/软件:

您好的团队、

目前、我正在使用 ADC12DJ5200RF EVM 以及 ADCxxDJxx00 GUI。

我们使用 JMode3 来测试 ADC 在 5.5GHz 输入频率和 4.8GSPS 采样频率下的性能。

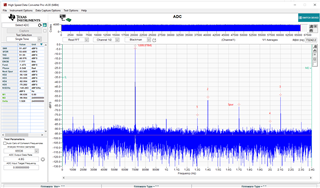

在默认模拟满量程范围 (800mVpp) 下进行测试时、本底噪声约为 85dBFS、SNR 为 51dBFS、HD3 为 53.6dBFS。

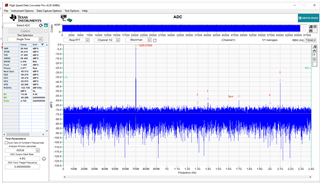

在 500mVpp 模拟满量程范围内、本底噪声增加至 65dBFS、SNR 为 29dBFS、HD3 为 38dBFS。

因此受到影响。

您能澄清一下本底噪声和满量程范围之间的关系吗? 和还提供了用于改善 上述配置的 SNR 和 HD3 的解决方案。