Other Parts Discussed in Thread: ADS1259-Q1, MSP430F2619, ADS1259

Thread 中讨论的其他器件: MSP430F2619、 ADS1259

工具/软件:

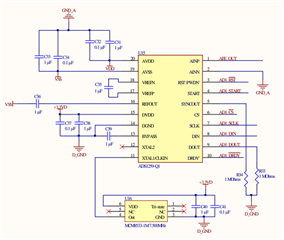

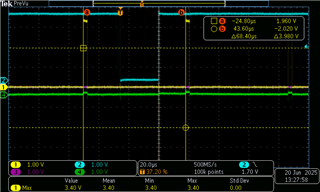

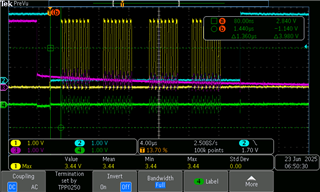

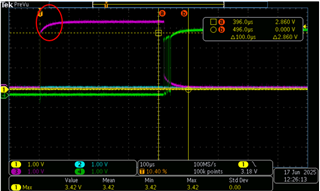

我目前正在开发一款包含 ADS1259-Q1 和 msp430f2619 MCU 的工具。 目前、我的硬件和固件能够使用芯片选择 (CS) 始终为低电平(使用 GPIO 引脚设置)读取有效数据、如下所示:

* START =黄色(已圈出)、DRDY =紫色、CS =蓝色、DOUT =绿色。

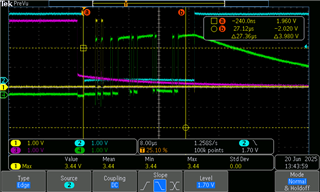

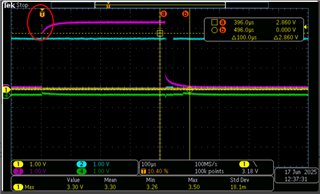

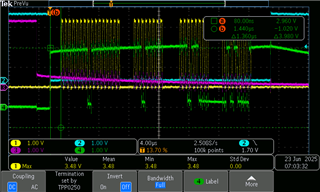

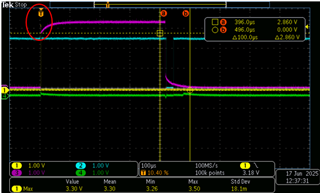

我正在为未来的设计做好准备、在该设计中、2 个 ADS1259-Q1 将位于一条 SPI 线路上(与单独的 CS、RST、START、DRDY 共享 SCLK、DOUT、DIN)。 我正在测试一种通信方案、该方案在一条 SPI 线路上使用 CS 和一个 ADS1259 进行准备。 不过、 启用 CS 时、我的 DOUT 保持非活动状态。 如下图所示:

* START =黄色(已圈出)、DRDY =紫色、CS =蓝色、DOUT =绿色。

一些注意事项:

- 这与在 CS 保持低电平时提供有效结果的硬件相同。

- 版本之间固件的唯一区别是 CS 是否在整个操作(第一个屏幕截图中的工作版本)中保持低电平、或者 CS 仅在读取/写入操作(第二个屏幕截图)中变为低电平。

- 数据表提到 CS 低电平与 SCLK 上升沿之间的最短时间为 50ns。 我在我的系统中测量了 300ns、并经过测试、延迟高达 15us、行为无变化。

- 已检查 ADS1259 和 MSP430 侧的引脚以确认通过的信号。

- MCU 使用 16MHz 外部时钟、ADS SCLK 使用设置为 2MHz 的 SPI 时钟

- ADS1259 寄存器设置(适用于这两种情况):

- CONFIG0 = 0x05:启用 SPI 超时、内部基准偏置

- CONFIG1 = 0xc0:校验和、启用超出范围标志(用于确认有效数据)

- CONFIG2 = 0x17:脉冲控制模式、14400sps。

- 偏移:未设置

- 设置为 RDATAC

在尝试使用 CS 时、我会寻找其他调试提示。 此外、当在一条 SPI 线路上使用 2 个 ADS1259-Q1 来设计系统时、我希望能考虑任何建议