工具/软件:

嗨、团队

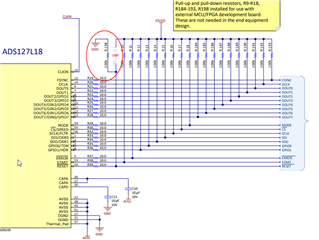

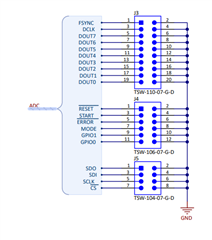

我正在使用 ADS127L18EVM 并希望与基于 FPGA 的系统连接。 目前、我们尚未开始与 FPGA 连接、刚刚开始测试 SPI 寄存器配置 EVM 中的读取和写入命令。 我们使用的是 LPC55s69 NXP 的微控制器、该微控制器能够以以下频率运行 1.8V 逻辑配置为 SPI 主器件。 根据数据表、我进行了以下连接。

| 引脚 | 相匹配 |

| 消耗量 | 短接至 IOVDD1.8V |

| /CS | LPC55s69 UC 中的 CS |

| SCLK | LPC55s69 UC 中的 SCK |

| SDI | Mosi in LPC55s69 uc. |

| SDO | LPC55s69 uC 中的 MISO |

| GND | GND |

。 SPI 模式 设置为 CPOL = 0、CPHA = 1。 SPI SCLK 设置为 12MHz。

目前我正在尝试读取 DEVICE_ID 我要发送 2 字节命令的寄存器-< 0x00 >。 但是 SDO 保持 高电平。 我尝试了从其他寄存器进行写入和读取、但这也失败了。 我做什么错了。 感谢您提供任何帮助。

注释 :否则、EVM 将正常工作。 我已经使用套件随附的 GUI 和 PHI 适配器验证了 ADC 采样和寄存器配置。 只是当与外部器件连接时、SPI 接头引脚不按预期工作。