工具/软件:

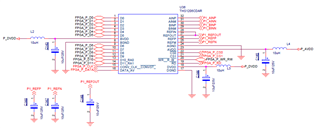

我正在尝试将 THS1206 与 AMD Artix 7 FPGA 连接。

ADC 在差分模式下配置为双通道。 当我尝试通过将 CR0 设置为 0c8h 来在自动扫描模式下运行时、ADC DATA_av 线路始终保持高电平。

执行的初始化过程如下:

1) 写入 CR1 401h。

2) 写入 CR1 400h

3.) 写入 CR1 402h(用于 FIFO 复位)。

4.) 写入 CR0 0c8h、

5.) 写入 CR1 410h。

对于同一序列、如果我在步骤 4 中写入 020h 或 028h(单个通道处于差分模式)、DATA_av 线路会根据需要切换、并能够看到输出。

我在这里做什么?

而