Other Parts Discussed in Thread: DAC39RF12EVM

工具/软件:

你(们)好

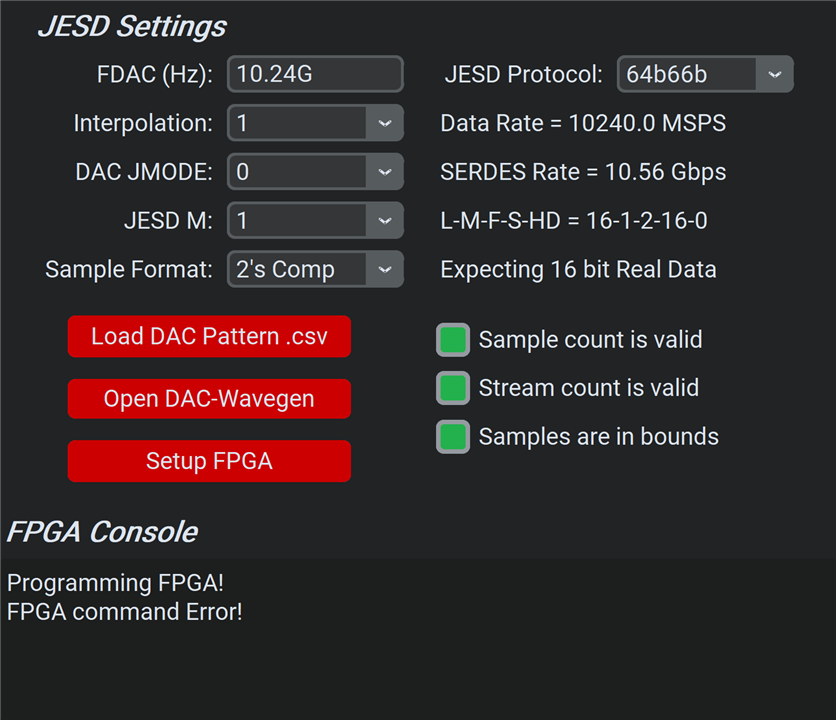

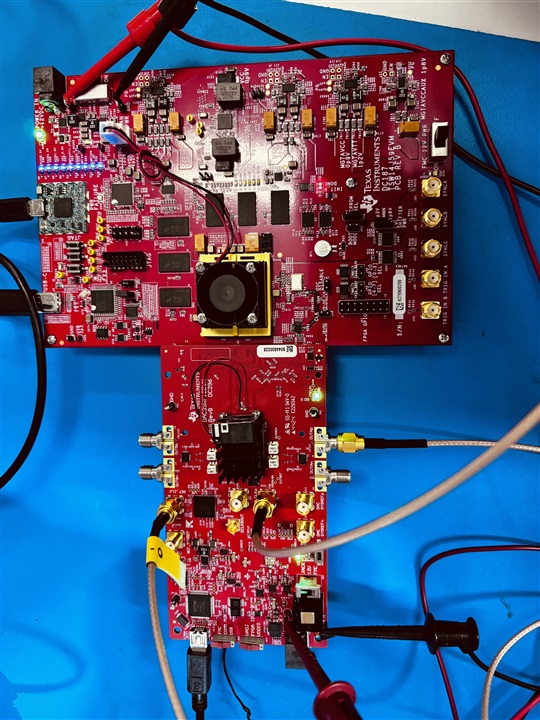

我按照手册中提供的步骤操作、使用连接器 J6 上功率级别为 10dBm 的 SMF 100A 信号发生器和连接器上的基准时钟@ 160MHz @ 12dBm 提供 DAC 时钟@10.24GHz。 我按照建议安装了所有应用程序。 FPGA (TSW14J59) 单独供电 (12V、3A)、将板上的 FMC 电源设置为关闭、而 DACEVM 使用另一个电源 (12V、3A) 供电。 我在 DAC 评估板上看到绿灯。

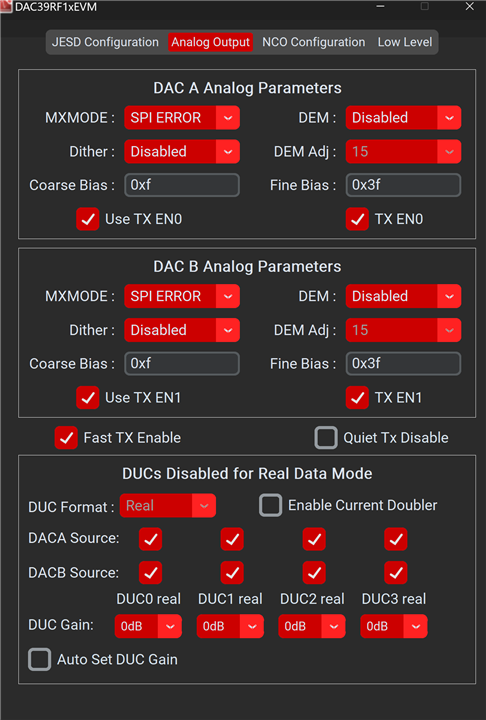

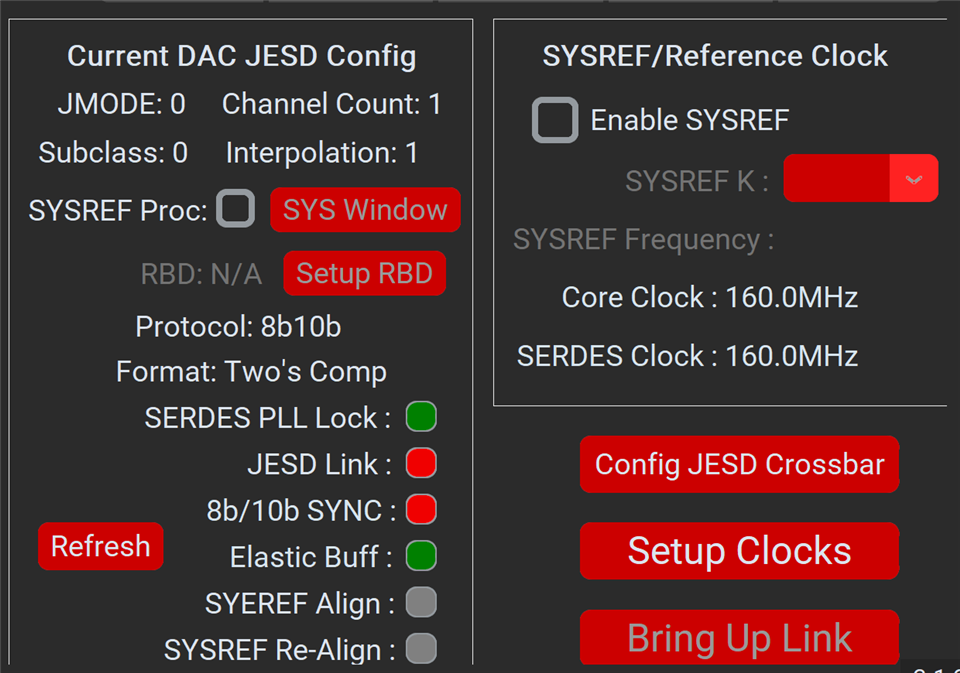

此后、我从 GUI DAC39RF12EVM 软件开始、按照建议的 J59 服务器启动并侦听端口所执行的步骤、按照 JMode0 中的建议对 DAC 进行编程、如所述、在 4GHz 时在频谱分析仪上看不到任何输出。

有人能帮助我做什么我错了,有什么要注意?

两个器件都位于 10MHz 同步时钟上。

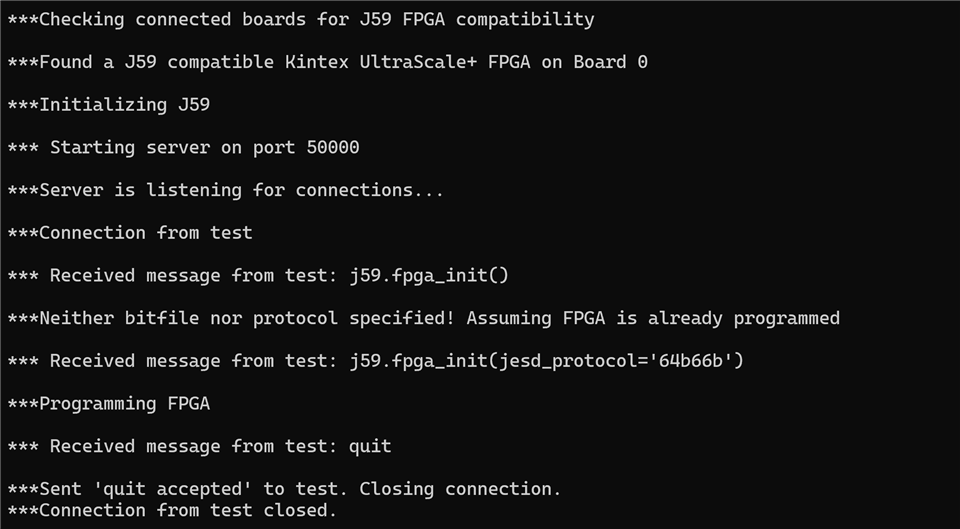

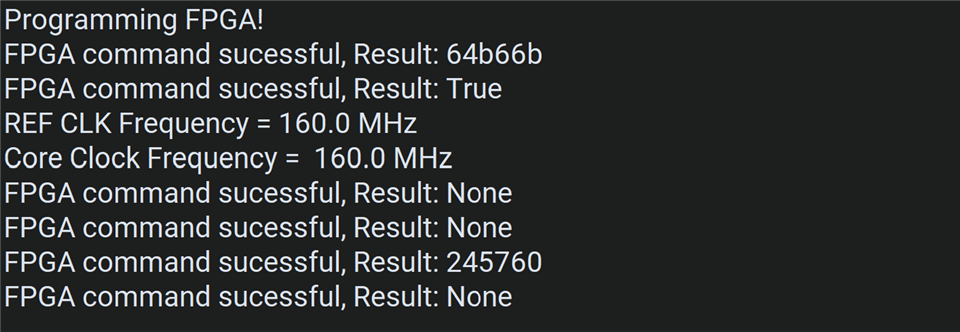

附件也是来自 J59 服务器的日志文件。

***调查互联 FPGA 的环境...

***检测到一个 FPGA。 电缆 ID 为 210251B73D74

***检查连接的主板是否与 J59 FPGA 兼容

***在板 0 上找到一个与 J59 兼容的 Kintex UltraScale+ FPGA

***初始化 J59

***在端口 50000 上启动服务器

***服务器正在侦听连接...

***从测试连接

***从测试收到的消息:j59.fpga_init()

***未指定位文件或协议! 假设 FPGA 已编程

***从测试收到的消息:j59.FPGA_INIT (jesd_protocol='64b66b')

***编程 FPGA

*** J59 FPGA 已初始化。 正在检查支持的协议

*** FPGA 加载 64b66b JESD IP

***从测试收到的消息:j59.jesd_set_link_rate (LANE_RATE=10560000000.0、gbtrefclk_rative=66.0 )

***将 PLL 基准缓冲器设置为 REFCLK0

***期望 PLL 参考频率为 160.0MHz

***选择的 PLL 为 QPLL0

***所有 PLL 已锁定。 PHY 就绪

***从测试收到的消息:j59.DAC_SET_JESD_params ('lmfs_params'、links=1、lanes=16 、channel=1、Frame_Octets =2、 Samples_Per_Frame Sample_Resolution = 16、Frames_Per_Multiframe = 32 、Channel_Resolution = 16、 JESD_Mode= 16、 HD_Mode= 0 Format_Twos_Complement = True、 去交错因子=无)

***设置 Tx IP 的 LMFS 参数

***通道映射和反转将设置为默认值

{'链接':1、

'Lanes':16、

'通道':1、

Frame_Octets:2、

Samples_Per_Frame:16、

Channel_Resolution:16、

'JESD_JESD' Sample_Resolution:16、

' Format_Twos_Complement ':正确、

'HD_Mode':0、

Frames_Per_Multiframe:32、

'MEMBlock' Blocks_Per_:1、

“摇摆“:1、

'LANE_MAP':[0、1、2、3、4、 5、6、7、8、9、 10、11、12、13、14、 15]、

“REVERD_LANES":“:[0、0、0、0、 0、0、0、0、0、 0、0、0、0、0、 0]、

“ACTIVE_LANES":“:[1、1、1、1、1、 1、1、1、1、1、 1、1、1、1、1、 1]、

'dedavert_factor':无}

***从测试收到的消息:j59.DAC_LINK_BRUPing()

***从测试收到的消息:j59.DAC_LOAD_BUFFER (csv_file='D:/tempfiles/v3.1.2/J59 Commander/DAC_TONES/temp.csv、start_address ='RAM1')

***已加载缓冲区。 缓冲区的总大小为 245760

***从测试收到的消息:j59.DAC_SETUP_PLAZATION (PLAYBACK_BUFFER_START_ADDRESS='RAM1'、 BUFFER_SIZE=245760)

***设置 DAC 回放缓冲区和参数

{'LANE_PLAYBACK_ORD':[0、1、2、3、4、 5、6、7、8、9、 10、11、12、13、14、 15]、

“Playback_buffer_start_address":“:“RAM1",“,</s>、

'Buffer_size':245760、

'Cycline_mode':true、

'TRIG_SOURCE':'SW'、

'TRIG_DELAY':0、

“start_on_multicambox":“:错误、

'WAIT_MULATION_BOUNDARY':FALSE}

***从测试收到的消息:j59.DAC_PLAYBACK_START()

***从测试收到消息:退出

***已发送“已接受退出“进行测试。 关闭连接。

***测试连接已关闭。