工具/软件:

您好的团队、

我有几个关于 DAC3171 运行的技术问题。 请您仔细回答一下。

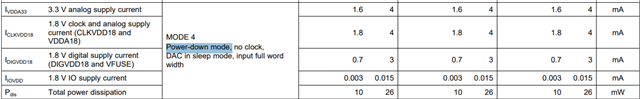

1.用户如何配置断电模式?

2.无时钟意味着用户停止将信号输入到 DAC 内核时钟 (DACCLKP/DACCLKN)?

3.数据表第 14 页中是否列出了任何降低功耗的配置(模式 1、模式 2、模式 3、模式 4)?

此致、

山本俊介

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Geoff:

感谢您的回答。 我收到了关于 DAC3171 的其他几个问题。 您能帮我回答吗?

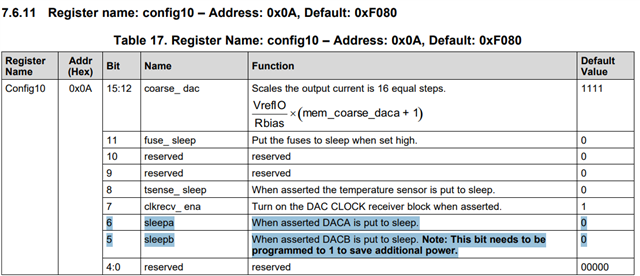

1.什么是 sleepa 位和 sleepb 位? 用户是否需要配置这些位来将器件置于省电模式?

2.从正常模式(模式 1 和模式 2)到断电模式(模式 4)需要多长时间?

3.要配置断电模式、用户是否需要先将 SLEEP 引脚设置为低电平还是高电平、DACCLKP/N 是否关闭?

此致、

山本俊介