工具/软件:

您好、

我们目前在菊花链配置中使用五个 ADS7066IYBHT 器件:

FPGA→ADC0→ADC1→ADC2→ADC3→ADC4→FPGA

我们正在尝试对0x800x8A每个 ADC 的 GENERAL_CFG 寄存器(地址:0x01)进行或写入、以启用内部基准并执行偏移校准。

使用的协议是 SPI-00(默认)、SCLK 频率为 1MHz。

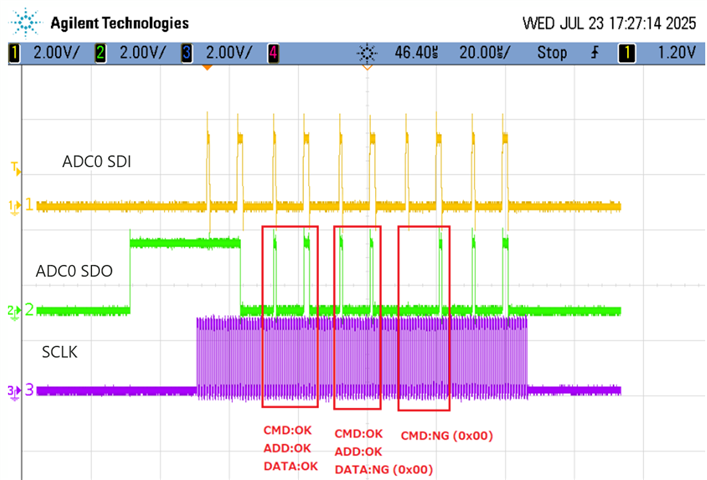

0x080180从 FPGA 向 ADC0 发送数据(24 位)后、ADC0 的 SDO 输出似乎显示了正确的命令/地址/数据时序。 但是、对于 ADC2、ADC3 和 ADC4、SDO 上数据输出的时序会错位、并且 GENERAL_CFG 寄存器写入不会成功(接收到的命令和数据)0x00。

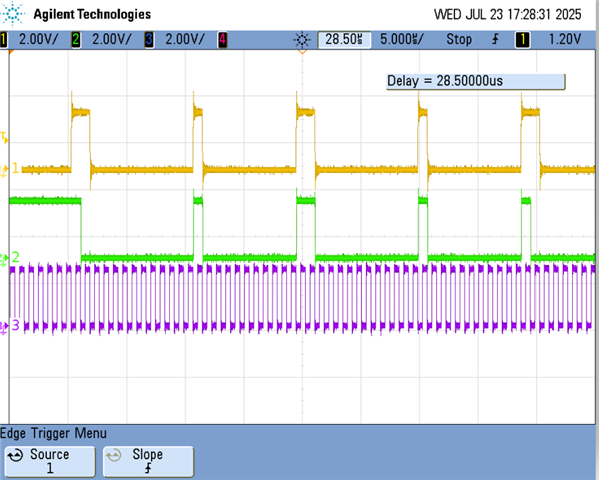

我们随附了显示此问题的示波器波形。

我们想确认以下几点:

① 关于 SPI-00 协议时序

在 SPI-00 模式下、ADC 在 SCLK 的上升沿锁存 SDI 数据、在 SCLK 的下降沿更新 SDO 数据是否正确?

② 关于寄存器初始化

我们当前正在 ADC 初始化期间设置以下寄存器:

-

GENERAL_CFG 寄存器 (0x01)= 0x8A

→GENERAL_CFG[1]:CAL = 1(已启用 ADC 失调电压校准)

→在 ADC 初始化过程中是否需要执行失调电压校准? -

OPMODE_CFG 寄存器 (0x04)= 0x08

Δ V OPMODE_CFG[3:→:CLK_DIV = 1000b(采样频率= 62.5kSPS)

如果必须配置其他寄存器才能在菊花链模式下正确运行 ADC、请告知我们。

③ 关于通信问题的假设

我们怀疑该问题可能是由于向所有 5 个 ADC 发送数据时 SCLK 时钟数量不足而引起的。

由于链由 5 个器件组成、因此我们认为在单次 SPI 传输中需要 24 位× 5 = 120 位 SCLK、才能通过所有器件正确传播数据。

但是、我们目前0x080180按顺序发送 24 位命令/地址/数据 () 5 次、这可能不足以让下游 ADC 通过 SDO 接收和传递数据。

④ 要确认的问题

-

在菊花链模式下写入 5 个 ADC 时、是否需要在单次传输中发送 120 个 SCLK 时钟?

-

或者、只要之后发送额外的 SCLK 时钟 (24 ×(N−1)= 96 位)以允许数据通过链传播、单独发送 5 组 24 位命令是否有效?

-

在菊花链模式下运行 ADS7066 时、我们是否应该注意任何其他时序或配置点?

感谢您的确认和支持。

可根据要求提供示波器捕获和电路原理图。 如果您需要更多详细信息、请告知我们。

此致、

Conor