主题中讨论的其他器件: ADS9229、 ADS9228

工具/软件:

你(们)好

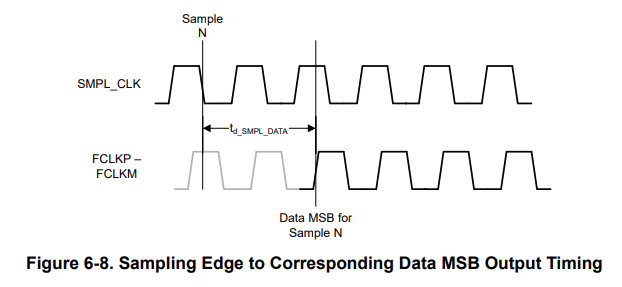

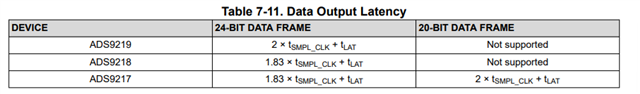

ADS9227 数据表的第 6.7 节列出了参数 TD_SMPL_DATA (延时时间:SMPL_CLK 下降至 FCLKP 上升)、最小值为 103ns、最大值为 112ns。

如果仅在 4.167ns 的时钟输出周期(使用 24 位输出字格式)下运行时该值才为真、这是否是正确的? (24 x 4.167ns =约 100ns)。 表前面的段落确实显示了“最大吞吐量“、因此我假设有 3ns 到 12ns 的额外延迟。

因此、说额外的延迟 与数据链路配置无关且这个 3ns - 12ns 适用于 ADC 的任何配置是否正确?

非常感谢您的帮助!