Other Parts Discussed in Thread: ADC12DJ5200RF

工具/软件:

尊敬的团队:

1.使用芯片: ADC12DJ5200RF

2、配置模式:双通道 5GSPS

3. 204 接口配置:使用 JESD204B 8B/10B、JMODE3

4、模拟信号输入:5G/2.5G/1.25G/0.625G/0.3125Gbps、总共 5 级

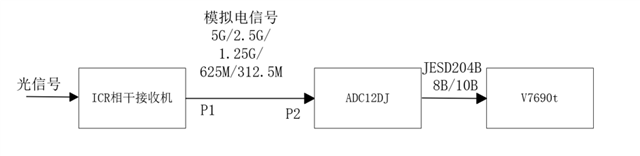

5.现象描述:客户使用此 ADC 在相干接收器 (ICR) 后进行数据采集。 当输入信号处于 5Gbps 的最高电平时、采用 QPSK 调试格式、I 和 Q 通道均为 2.5Gbps、因此满足 2 倍采样关系。

低速第四档采用 BPSK 调制格式、客户没有更改 ADC 的工作模式、固定为使用双通道 5GSPS 模式。

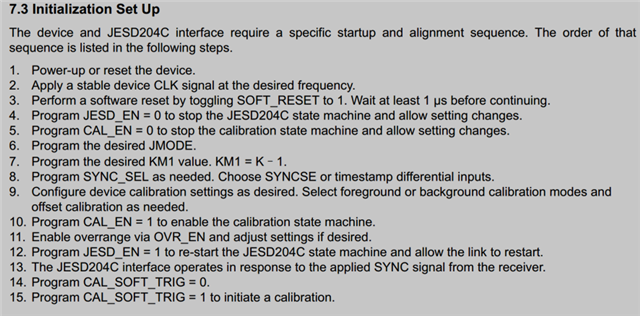

有关 ADC 的初始化配置、客户可以参阅 IC 数据表的第 7.3 节。

现在已经发现、接收信号的灵敏度与算法的理论值相差很大(约 3-7dB)、并且随着输入信号速率的降低、该差值变大。 例如、在 5G 速度下、与算法的理论值存在 3dB 的差异、在 0.625G 下、时间差为 6dB。

灵敏度测试方法是在链路中添加一个衰减器并增加衰减、直到误码率超过 FEC 纠错限制。

客户使用高速示波器从 ICR 后端和 ADC 前端(图中的位置 P1 和 P2)收集信号、并对 Matlab 中的数据执行算法处理。 研究发现、这里也有一些下降、但没有造成如此大的灵敏度差异。

FPGA 接收到的 ADC 收集的数据通过 Vivado 导出到 ILA 文件、并由 MATLAB 中的算法进行处理。 结果发现差值为 3-7dB。 此处 ADC 收集的数据会显著降低信号质量。

6.提问

客户仅参考第 7.3 节来配置和使用 ADC。 还有什么可以改进的吗? 它可能对其灵敏度问题有所帮助。

谢谢你

BR