Thread 中讨论的其他器件:THS4551、 REF7025、

工具/软件:

您好、TI 团队:

我对 ADS127L11 有类似的设计、与前面提到的相关问题类似。 现在、我通过差分对使用 REF7025 电源 2.5V REF 至 REFP 和 REFN。并将寄存器设置为 2 倍输入范围。我是否可以将 REFN 更新为 AGND、(AGND 也是 THS4551 的 GND)、或者 REFN 必须升级为 AVSS??或两者都可以?

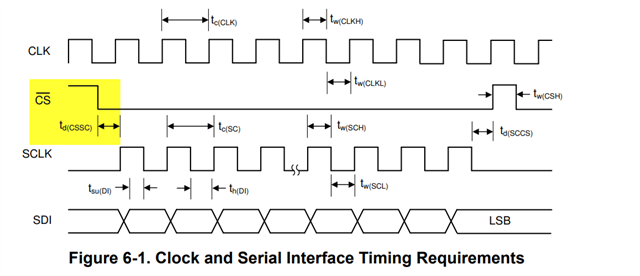

另一个问题是:我能否将输入时钟更改为 CLK 引脚、以获得特殊的输出数据速率我需要的是什么?如果我可以、有任何我应该 特别注意的事情、以获得此芯片的最佳精度和噪声性能?

希望你忏悔、谢谢!