主题: ADS127L21 中讨论的其他器件

工具/软件:

您好:

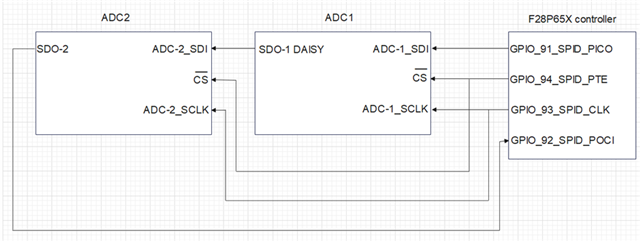

我目前正在研究通过 SPI 将两个菊花链模式下的 ADS127L21B ADC 与 TMS320F28P650DH6(C2000 系列)微控制器连接在一起。

按照前面关于寄存器配置的指导、我实现了对器件寄存器进行写入的建议方法。 具体而言、我正在尝试配置寄存器 0x0B (MODE0)、以便将两个 ADC 设置为仅数据输出模式。

但是、在两个 SPI 帧期间、我始终收到来自 ADC 的输出 0x000000FFFFFF、这似乎不正确。 这意味着寄存器写入可能未生效、或器件未按预期响应。

密钥详细信息:

两个 ADC 都以菊花链模式连接

SPI 接口:TMS320F28P650DH6 上的 SPID

正确管理芯片选择 (CS)、START、RESET 和 DRDY 信号

DRDY 受到监控并同步

我尝试将 0x0B 写入 MODE0 寄存器(地址 0x0B)

使用逻辑分析仪验证了 SPI 信号—观察到 MOSI 活动、但 MISO 始终返回 0xFFFFFF

我非常感谢对可能出现的问题有任何见解或建议。

如果需要任何其他信息(代码片段,逻辑分析仪捕获结果等)、请告诉我。

因为两个 ADC 都配置在中 菊花链模式 、我想确认正确的 DRDY 引脚以监控数据就绪指示。 目前、我将两条 DRDY 线路 (ADC1 为 GPIO11、ADC2 为 GPIO61) 连接到 MCU。

在菊花链配置中、需要对其进行监测 两个 DRDY 引脚 或正在监视 仅链中最后一个 ADC 的 DRDY 引脚 (ADC2) 足以实现同步?

我的理解是、在菊花链模式下、两个 ADC 同时采样、并通过链串行传输数据。 因此、使用 仅限 ADC2 的 DRDY (GPIO61) 应该足够了。 请您确认一下。

如果您对导致恒定 0xFFFFFF 读取问题的原因有任何见解或建议、我们将不胜感激。 请告诉我、代码片段或逻辑分析仪波形等其他信息是否有用。

提前感谢您的支持。

此致、

Divyesh Patel