主题:ADS1258 中讨论的其他器件

工具/软件:

您好、

我的客户希望使用外部时钟、但不确定时钟信号所需的逻辑电平高度。

您能否对时钟信号提供其他要求(频率稳定性,抖动等)?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我的客户希望使用外部时钟、但不确定时钟信号所需的逻辑电平高度。

您能否对时钟信号提供其他要求(频率稳定性,抖动等)?

谢谢

您好 Franziskus、

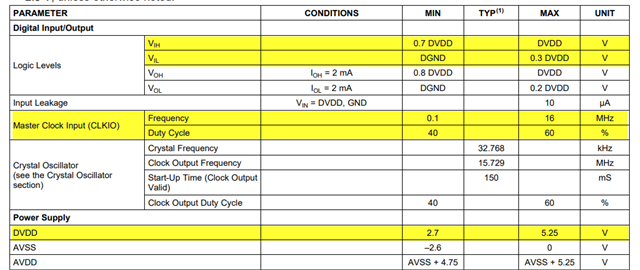

时钟输入以 DVDD 电源为基准并且应是标准 CMOS 电平。

时钟频率可在 0.1MHz 至 16MHz 的范围内、需要 40%至 60%的占空比。

实际上对时钟的“稳定性“没有要求、但输出数据速率将与时钟频率成正比、因此应考虑这一点。

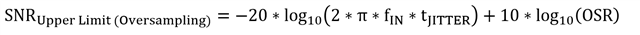

时钟抖动会导致测量交流信号时的噪声增加、具体取决于输入信号频率和 ADC 内部的过采样量。 与抖动相关的 SNR 的基本公式为:

其中、对于特定数据速率、SNRupperLimit 应比 ADC 的 SNR 高 10dB。 OSR 是过采样率。 ADS1258 数据表没有直接指定该值、因此我在下面提供了该值。

| DRATE[1:0] | 输入噪声 (uVrms) | SNR (dB) | OSR |

| 11. | 12 | 107.7. | 64 |

| 10. | 7.9. | 111.3. | 256 |

| 01. | 4.5. | 116.2. | 1024 |

| 00 | 2.8. | 120.3. | 4096 |

例如、在 DRATE 范围为 11 (f-CLK=10kHz 时为 125000sps 16MHz) 时、假设您要测量频率为 f-in=10kHz 的输入信号。 在此配置中、ADC 的近似 SNR 约为 107.7dB、因此将 SNR 上限设置为 117.7dB、并求解 t-jitter:

117.7 =–20*log (2*PI*10000*t-jitter)+10*log (64);求解 t-jitter

T-jitter = 166ps-rms、几乎任何市售的振荡器都可以满足该要求。

如果您只想测量直流信号、其中通常假设带宽在 0.1Hz 至 10Hz 范围内、则产生的 t 抖动= 166nsrms。 任何简单的 RC 振荡器通常都可以满足此要求。

有关更多详细信息、请参阅该 TI 高精度实验室视频:

https://www.ti.com/video/6360889031112

此致、

Keith Nicholas

精密 ADC 应用