主题中讨论的其他器件: DAC8830、 TPS3840、TL431、DAC8740H

工具/软件:

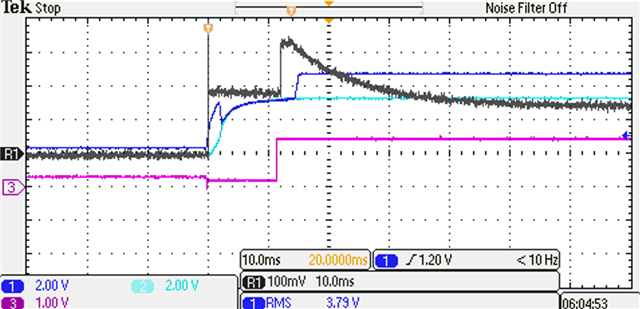

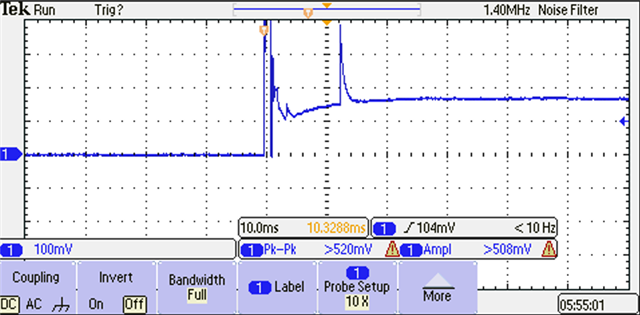

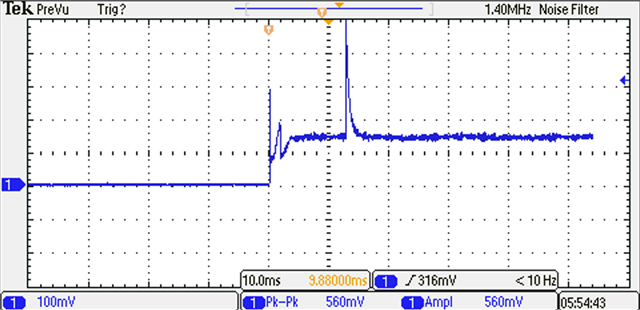

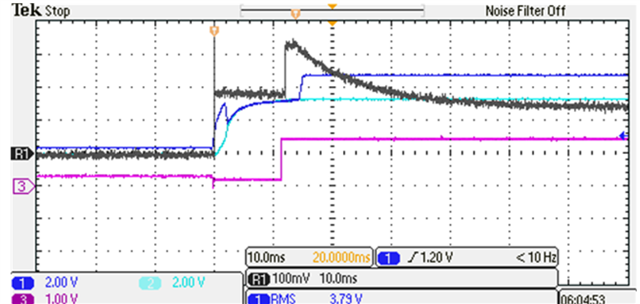

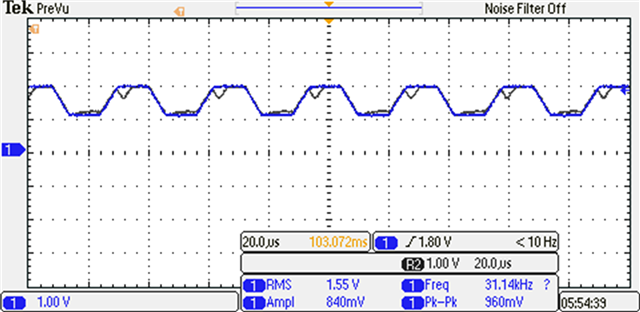

从使用内部(蓝色)基准更改为外部(黑色)基准时、我的 MOD_OUT 信号会失真。(相应地选择了 REF_EN)

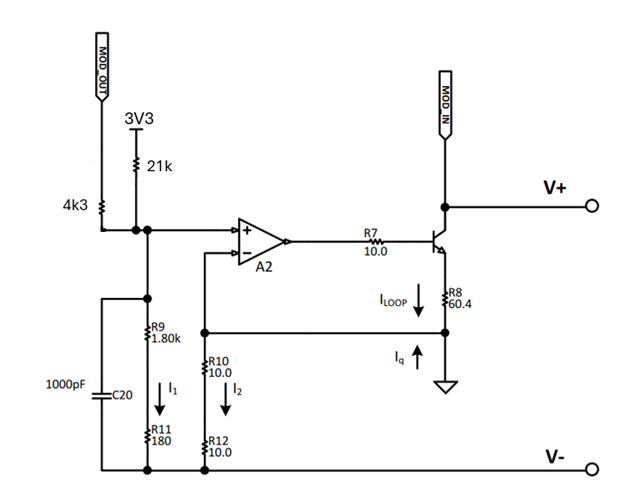

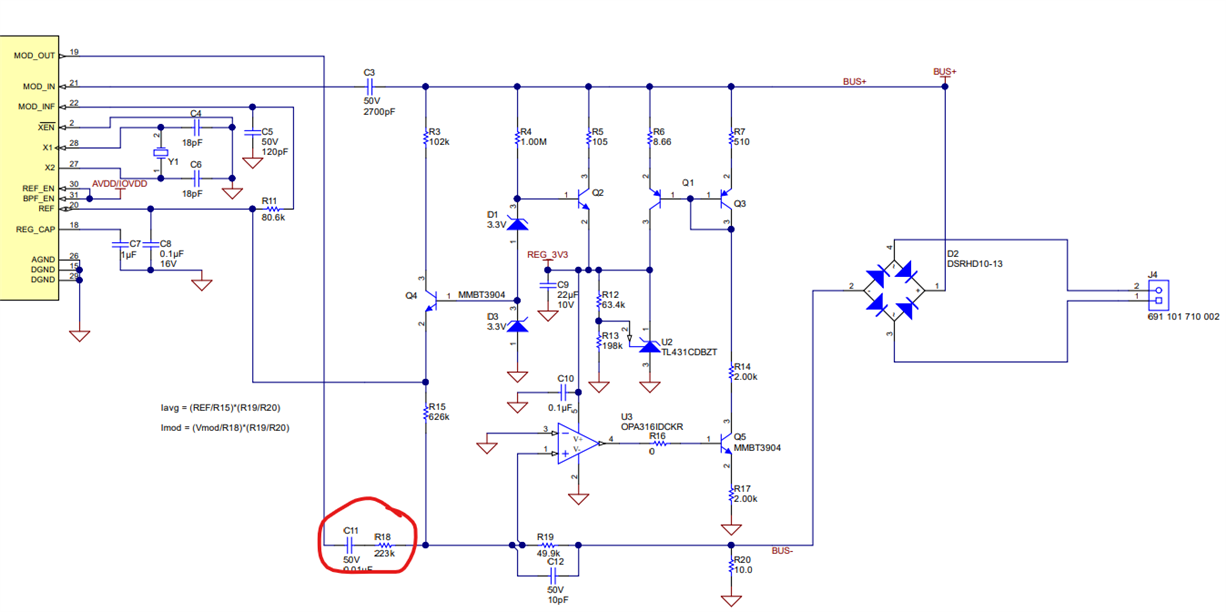

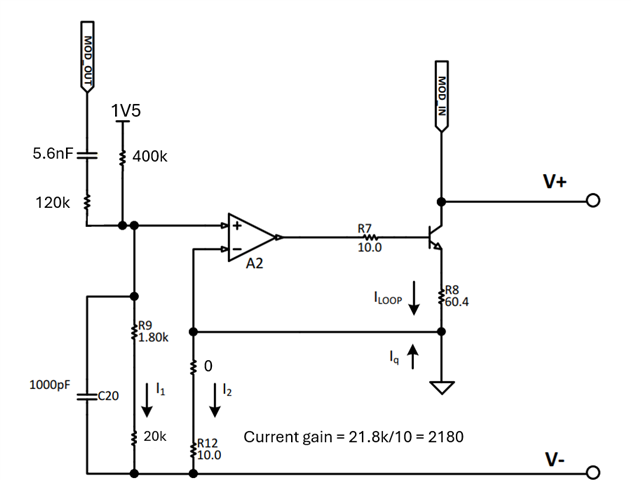

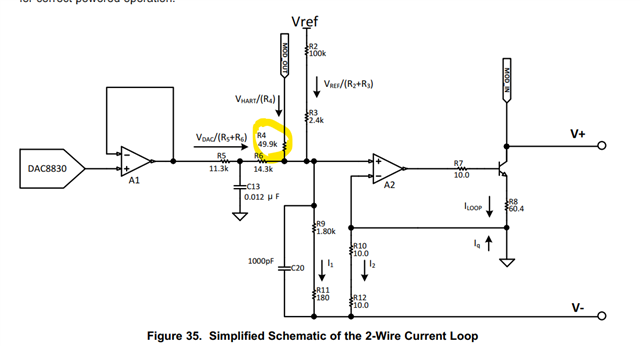

MOD_OUT 信号驱动 2 线电流环路电路、如 DAC8742H 数据表中的建议

当 我从 2 线电流环路电路断开 MOD_OUT(移除 R4)时、MOD_OUT 信号可以通过外部基准提供

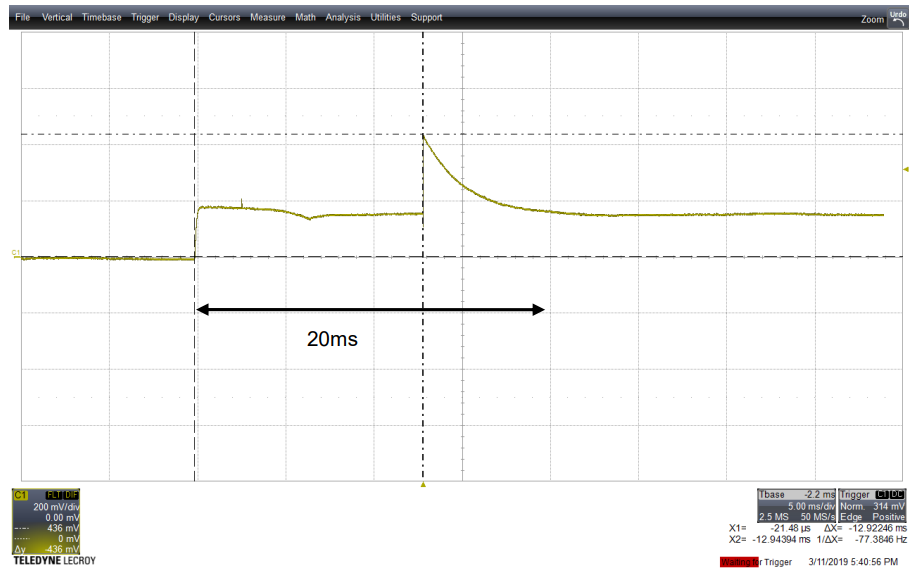

当我通过增加 R4 来减小 FF 电流时、 MOD_OUT 信号 可以与外部基准配合使用

当我将输入外部基准从 2V5 增加到 3V3 时、 该信号也可以与外部基准相同

我的问题是:

- 有关外部基准内部电气特性(最大/最小输入电流,输入阻抗)的更多详细信息

- 任何只应使用外部基准的特定情况

- 如果我将 3V3 用作外部基准、芯片是否会损坏