Thread 中讨论的其他器件:ADS127L18

工具/软件:

尊敬的专家:

我的客户推荐的是 ADS128L18EVM-PDK、但有一个问题。

如果您能提供建议、我将不胜感激。

-----

我目前正在使用 ADS127L18EVM 电路作为参考进行设计。

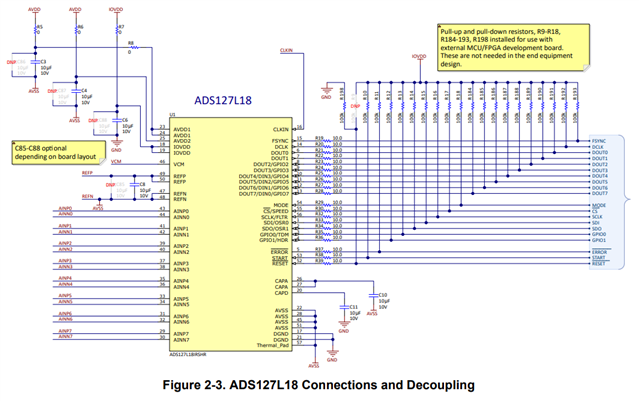

(1) 在 ADS127L18 EVM 中、下面的图 2-3 显示了 10Ω 电阻器 R19 至 R39。

100kΩ 电阻器 R9 至 R18、R184 至 R193 和 R198 有哪些用途?

(2) 在我们的示例中、ADS127L18 的输出将直接连接到 FPGA。

此时、我直接连接到 FPGA、因此我知道移除 10Ω 和 100kΩ 电阻器不是问题。

这种理解是否正确?

——

感谢您提前提供的大力帮助。

此致、

Shinichi