Other Parts Discussed in Thread: AFE58JD48

工具/软件:

大家好:

我目前正在处理一个将 AFE58JD48 集成到我们电路板中的项目。 我使用 FPGA 与 AFE58JD48 进行 SPI 通信。

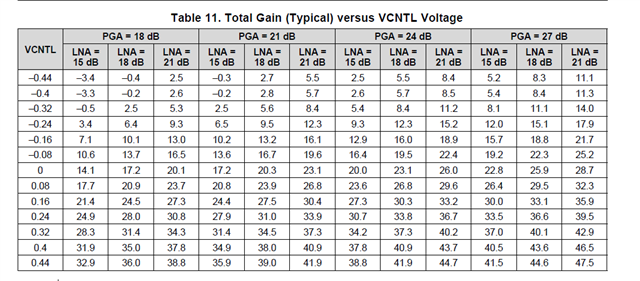

->当我对 VCA 部分(地址 0xC5 至 0x75E4)写入寄存器时 (地址 0xD1 至 0x588c)、要设置 LNA=15dB、PGA=18dB、VCNTL=–0.31V 、图片中相应的总增益为 0dB、但我的实际仿真为–6dB。

在其他 LNA、PGA 和 VCAT 的设置下、总增益始终减少 6dB。

我找不到需要在手册中配置的更多寄存器。 如何正确配置 VCA 寄存器? 您能为我提供正确的配置吗?

感谢你的帮助