请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC12J1600主题中讨论的其他器件:TSW12QJ1600EVM

工具/软件:

您好、

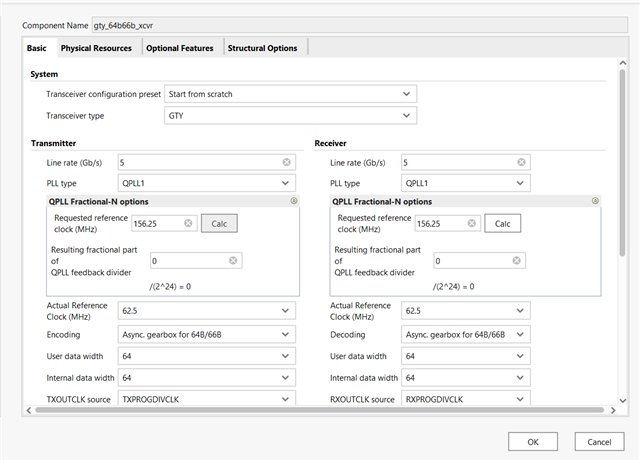

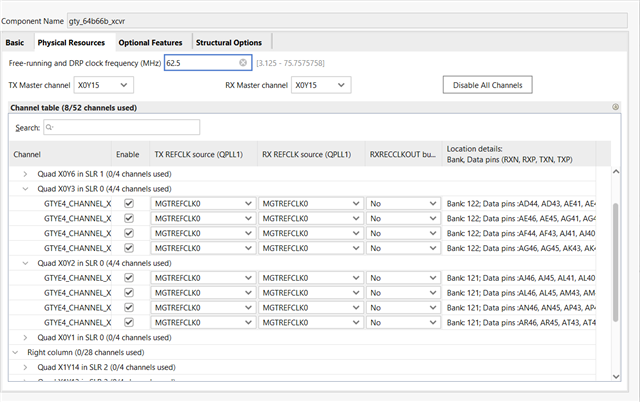

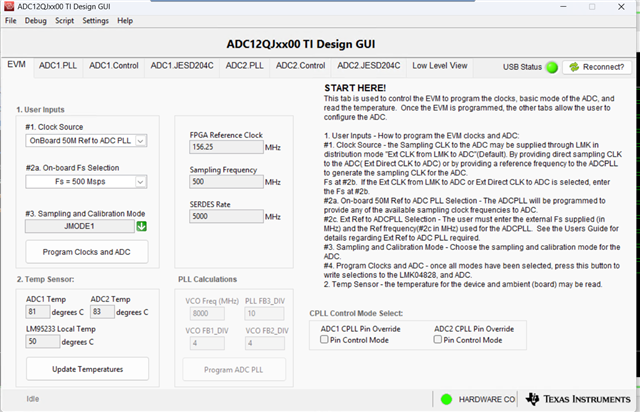

我似乎无法将 QPLL 锁定在我正在进行的设计中。 我使用一个 连接到 Xilinx VCU118 开发 BD 的 TSW12QJ1600EVM。 我已经映射了正确的引脚排列、已经验证我收到了 ref clk、并认为我已正确设置了它但它无法锁定。 我已经尝试了 QPLL0、QPLL1 和 CPL、但没有什么会锁定。 下面是我使用的 GT xcvr 设置和 ADC GUI。 我是否缺少复位序列?