工具/软件:

尊敬的 TI 团队:

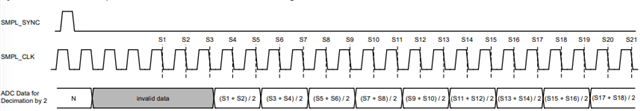

我 在两种不同的配置中执行了一些 ADC 延迟测量(SMPL_CLK 到数据通道上的数据)。 我对我测试的第二种配置中不了解的延迟有疑问。

我将方波信号发生器连接到 ADC 输入、并检查 ADC 输出端的数据流以查看数据中的阶跃。

案例 1: 禁用 2 通道输出和抽取

ADC 的 配置方式如下:

寄存器 0xFB -> 0x0000

寄存器 0x0D -> 0x2382

在本例中、我测得的延迟接近 112ns、抖动范围为 0ns 至 50ns。

50ns 的抖动是合理的、因为方波信号与采样时钟不同步。

112ns 对应于数据表中指定的延迟(第 11 页、TD_SMPL_DATA)、因此测量结果似乎是正确的。

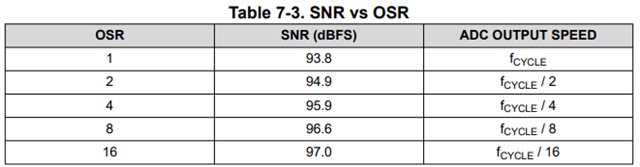

用例 2:1 通道输出和抽取 设置为 2 个样本取平均值

ADC 的 配置方式如下:

寄存器 0xFB -> 0x0002

寄存器 0x0D -> 0x23C2

在本例中、我测得延迟约为 225ns、抖动为 0ns 至 100ns。

100ns 的抖动是合理的、因为我们要在 50ns 的采样周期内对两个样本求平均值。

但是、我不明白为什么延迟增加了约 113ns。

您知道造成这种较高延迟的原因是什么吗?

启用抽取是否会增加延迟?

期待您的答复、