工具/软件:

尊敬的支持团队:

我希望实现与外部 10kHz 信号上升沿同步的恰好 10kSPS 采样率。

电路板配置:

- FPGA 连接到 ADS131M02

- 2 个 ADC 输入通道

- 单端输入:仅 AINnP (AINnN 连接到 GND)

我的策略:

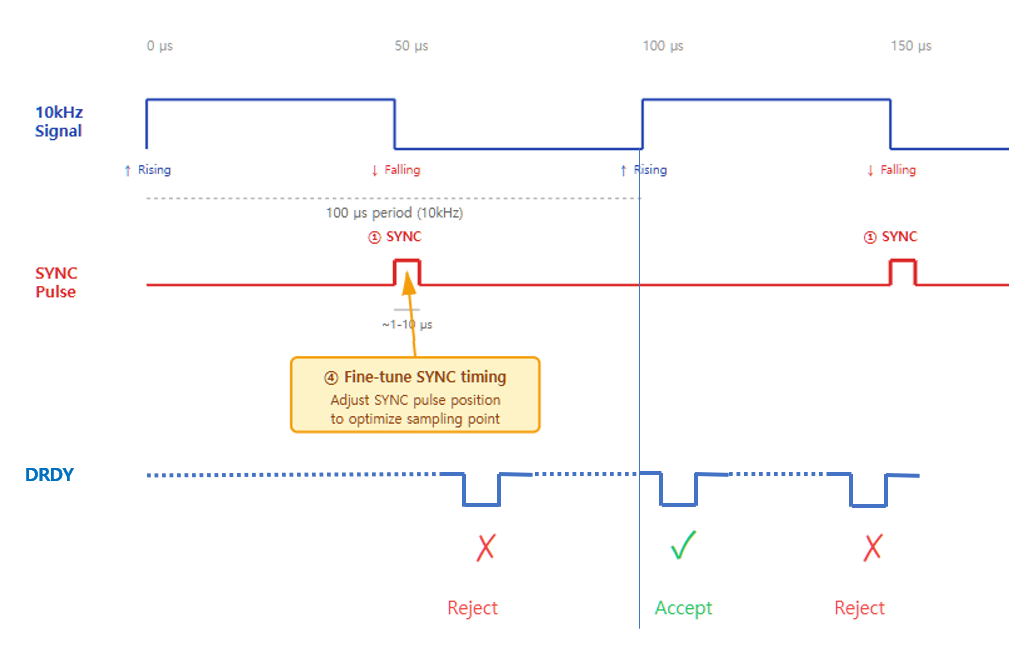

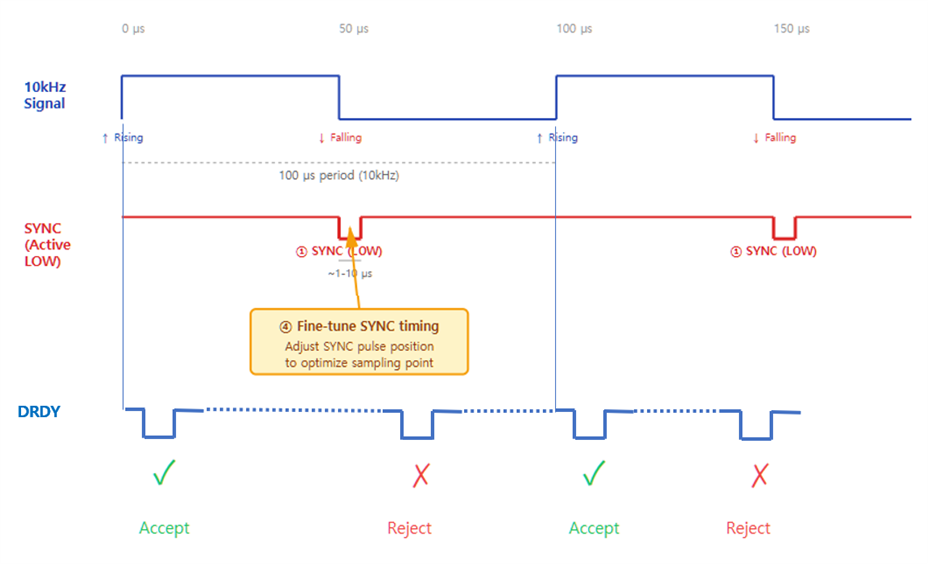

- 在连续转换模式下将 ADC 配置为 64kSPS

- 发送同步脉冲至外部 10kHz 信号的下降沿

- 在每个 DRDY 下降沿读取所有 ADC 样本

- 仅接受在 10kHz 上升沿之后立即采样的 ADC 数据

- 调整生成 SYNC 脉冲的时间、以微调每个 10kHz 周期内采样发生的位置

问题:

- 这种做法是否合理和可行?

- 是否有建议的最佳实践或我应该注意的潜在问题?

- 相位校准在该应用中是否有用?

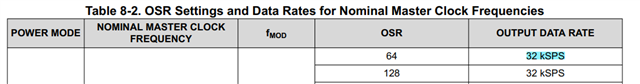

BTW 数据表的表 8-2 中似乎有一个拼写错误(SBAS853A–2020 年 1 月–2021 年 4 月修订)

我认为 OSR 64 对应于 64kSPS

感谢您的帮助。

此致、

Jason Lee