工具/软件:

你好、团队

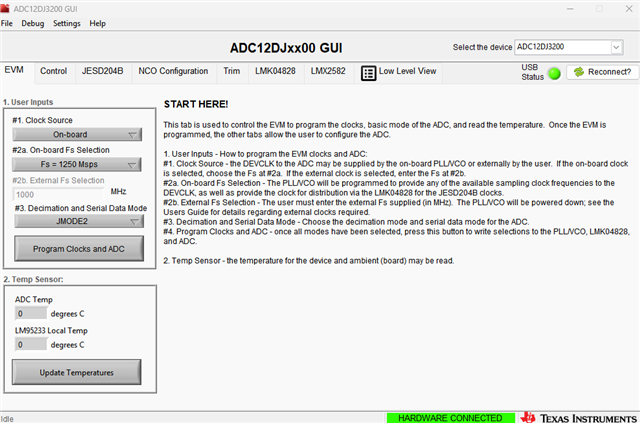

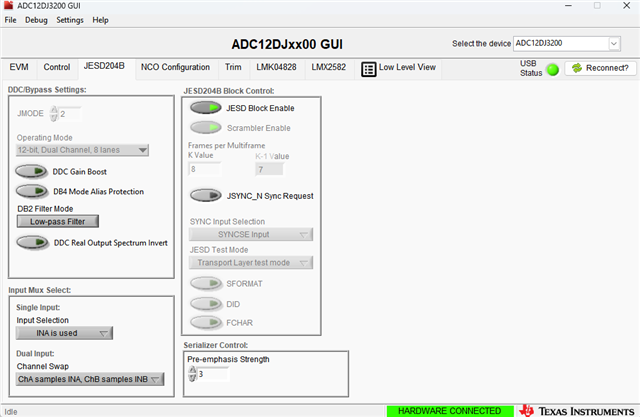

我正在测试 ADC 与 FPGA 在 JESD204B 子类 1 中的互操作性。 我从 4 通道设计开始、其中我为 JMODE 2 设置 ADC、其中 F=8、K=4。 FxK=32、由于我的接口为 32 位 (32/4=8)、因此 LMFC 边界为 8 个时钟周期。 对于子类 1、我也会在 ADC 寄存器下方明确设置。

0x2B0 01

0x29 70

问题:从 SYNC 置为无效到第一个 ILA 数据的时间会改变下电上电到下电上电、从而跨越 LMFC 边界、有时会导致子类 1 确定性延迟故障。 我们的 LMFC 边界为 8 个周期、因此我们预计每个通道上的数据在 8 个周期内。 这里没有车道偏斜,下面的说明。

为了计算从 SYNC 置为无效到第一个 ILA 数据所需的时间、我们运行对应每个通道的计数器。 每个通道上的计数值在本例中是相同的。

例如

首次下电上电时、每个通道的计数值为 0x0D、JESD 在 n 个 LMFC 边界上提供数据输出

然后在第 n 个下电上电期间、计数值= 0x15、第 n+1 个 LMFC 边界上的 JESD 数据输出。 这违反了子类 1 的要求。

请注意、直到我的计数值为 0x14、JESD 才在 n 个 LMFC 边界上提供数据。 问题在于计数值= 0x15 时。

是否知道为什么我们在 FPGA 上看到的数据具有 8 个周期下电上电与下电上电的最大差值、从而调节 LMFC 要求?

如果我遗漏任何内容、请告诉我。

-TRS