Other Parts Discussed in Thread: DAC63002, MSP430F5659

主题中讨论的其他器件: MSP430F5659

我之前发布了一个类似的问题、但没有收到回复、因此我正在再次发帖。

我目前正在使用 DAC63002、其外部基准电压连接到 VREF 引脚。 DAC 通过 SPI 通信从 MSP430F5659 MCU 接收数据。

在正常通信条件下、VREF 引脚几乎不消耗电流。 但是、当发生通信错误时、大电流流入 VREF 引脚、导致基准电压下降。

以下是我观察到的情况:

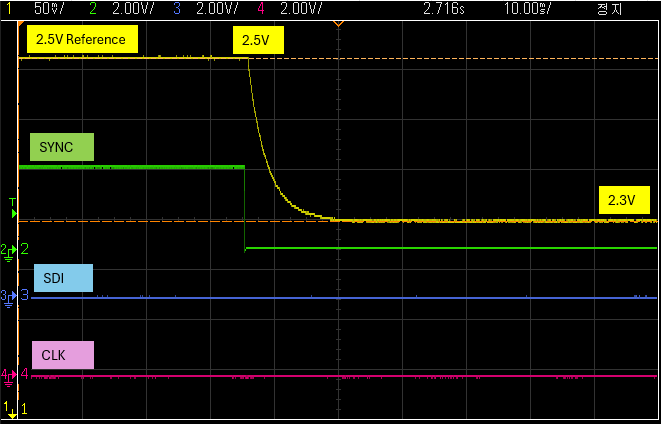

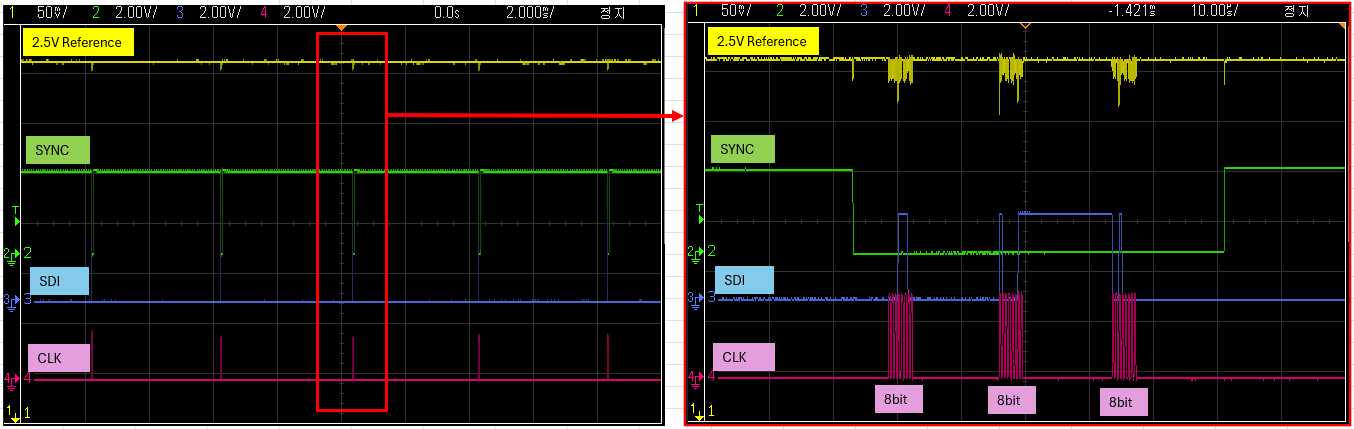

正常运行:

MCU 通过 SPI 发送 3 组 8 位数据(共 24 位)、同步信号在传输后立即关闭。 在这种情况下、基准电压保持稳定、没有大电流流入 VREF 引脚。

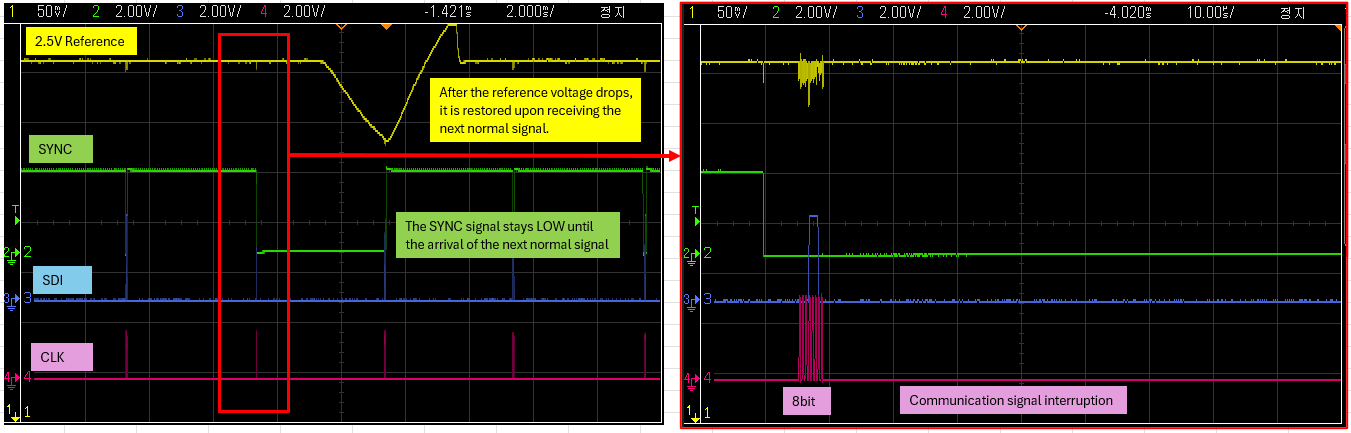

错误条件:

仅发送一个 8 位数据包后、传输会中断、这意味着不会将完整的数据传送到 DAC。 在此状态期间、SYNC 信号保持开路、大电流流入 VREF 引脚、导致基准电压下降。 只有在再次接收到正常信号后、电压才会恢复。

我的问题是:

当发生通信错误并且 SYNC 信号保持开路时、为什么电流流入 VREF 引脚?

是否有办法可以防止即使发生通信错误、基准电压也会下降?

当然、理想的解决方案是完全消除通信错误、但尽管进行了各种尝试、但它们仍会间歇性发生。 因此、我正在寻找一种权变措施或保护措施、以确保即使在此类错误期间 VREF 电压也能保持稳定。

任何建议或见解都将非常感谢。

谢谢你。