“线程: 测试”中讨论的其它部件

您好,

在我的 dign 中。 ADS42lb49在 DDR 模式下工作, 当采样200mV 方形信号时 LVDS 数据信号有一些问题。 由于 ADS42lb49 输入 Vpp 最大值为2V,因此当向 INAP/M 输入200mV 信号时,DA12P/M 应保持0, 但我在 DA12P/M 中捕获了备用0/1信号。我忘记存储波形, 以后会上传。

首先,让我介绍一些测试条件。

已 启用连接到 FPGA 和 FPGA 内部100ohm 终端的1/ADS42lb49 LVDS 输出时钟/数据信号。

2/电源正常,AVDD3.3,AVDD1.8,DVDD1.8全部 正常。

3/ads42lb49输入 时钟 是交流耦合的,其端接电阻接近 ads42lb49,为100ohm。输入时钟差动为800mV 和200MHz。

4无信号输入到模拟 Porta&B

5/SPI 设置如下,SPI 读/写正常。

0x08 0x01//首先重置

0x08 0x08//disable CTRL1/2 power down control (0x08 0x08//禁用 CTRL1/2电源关闭控制)

0x15 0x01//DDR 模式

0x20 0x01//禁用 CTRL1/2断电控制

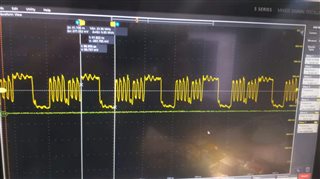

0x0F 0x44//run 数字斜率测试 模式。 下面是通道 A DA0P (引脚42)波形,因此 ADS42lb49的数字 数据块输出正常。

当模拟输入信号示例时,除 sett 0x0F 至0x00外,所有设置都相同。

顺便说一句,INAP/M 的模拟信号输入 如下所示,但 DC 耦合,INP 共模电压为1.9V,INM 为1.85V。我不知道 DC 对夫妇是否会导致一些问题。

另一个问题是 引脚29/30, 外部同步输入。 如果未使用,请将 SYNCINP 连接到 GND,将 SYNCINM 连接到 AVDD。 引脚29/30应直接连接到 GND/AVDD 或通过上拉/下电阻器连接。

您可以在此处共享 EVM 原理图。谢谢!