Other Parts Discussed in Thread: ADC32J42

我不确定如何在 ADC32J42上驱动 n ü~同步界面。 数据表未给出差分电压规格;仅提供 VHI,VLO 和 VCM。

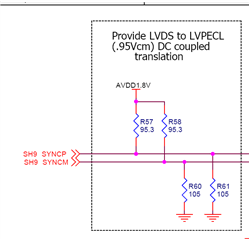

评估板声明“为 LVPECL DC 耦合转换提供 LDVS”有点混淆:该板以50欧姆至0.95V 的电阻终止~Ω 同步的每一段,这不适合任何一个已注意到的标准的直流耦合。

我计划直接与 Xilinx Zynq-7000系列 SoC 连接。 我有与 LVDS 兼容的 I/O 可用:VCM 为1.25V (典型),差分输出电压为350 mV (典型值-因此逻辑高为+350 mV,逻辑低为-350 mV)。 请参阅随附数据表(ds191*.pdf)的第14页表15。

我要指出,这一问题在 e2e 论坛上持续了六年,但没有明确的解决方案。 以下帖子表明 LVDS 驱动器应该正常,但 TI 尚未发布更新的数据表或任何明确的指导。

ADC32J42数据表:

ADC32J42评估板:

e2e.ti.com/.../ds191_2D00_XC7Z030_2D00_XC7Z045_2D00_data_2D00_sheet.pdf