线程中讨论的其他部件:测试, TSW14J57EVM, DAC38RF82EVM, DAC38J84EVM, ADC12DJ5200RF, TLK3101, TSW14J56EVM

您好,

我们希望测试一个 JESD204B 链路,用于在量子计算机内对经典数据状态进行源转发。

探测器发出小型模拟信号(这些脉冲的射频放大后为~10s-100s mV) 我们希望在光纤上发送检测位,在另一端接收检测位,以控制交换机的路径并驱动其选择线路。

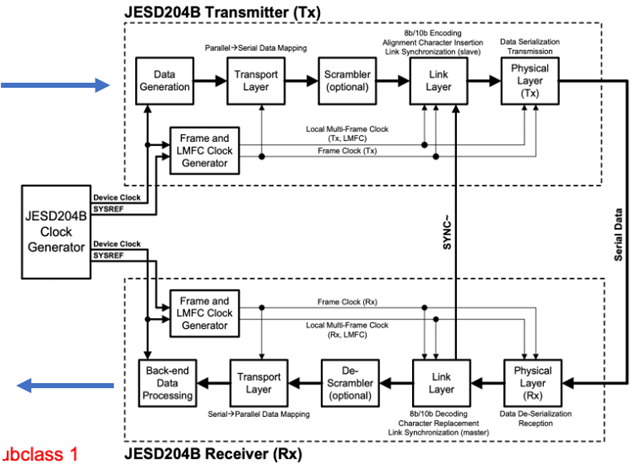

我们希望使用 JESD204B 链接来实现这一目标。 您是否有具有 ADC 和 DAC 以及 TX JESD204B 和 RX JESD204B 的串行映射,编码和同步以及序列化的评估板? 可以使用我们的组件快速设置并使我们能够测试此类链接的内容? 支持 GUI 和 FPGA 等...?

谢谢,