您好,

我希望您在使用交错模式时确认输出行为。

数据条件是我们逐个输入DAC A和DAC B的数字数据。

*根据数据表, 以下章节说明交错模式的行为。

7.3 3单总线交错数据接口和计时

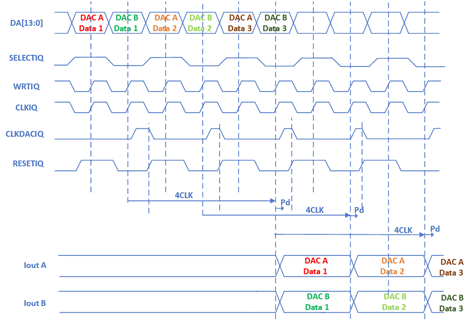

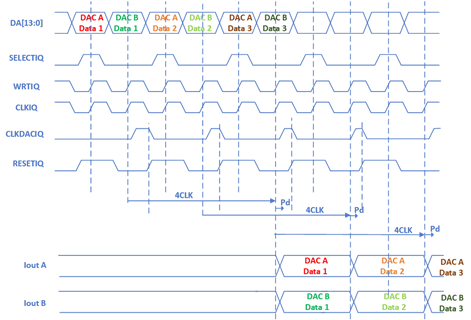

对于本节,我理解上述句子的图示。

1.当RESETIQ变为高电平时,来自分频器输出的DACCLKIQ (div /2)变为低电平。 但是,通过 WRTIQ的上升边缘来维护“DAC A Data 1”。

2. 当RESETIQ变得低时,DACCLKIQ将随CLKIQ的上升而上升。 在4CLK (tlat)更新+ PD之后,将为每个输出端口输出DAC A数据1和DAC B数据1。

对于DAC数据2和3,也将继续如此。

然后我有以下问题。

问题1. AF首先,我的上述理解和数字是否正确?

问题2. 如果 Q1正确,我的理解是,当用户尝试将DAC输出A和DAC输出B配对时,即使在最快的情况下,数据速率也应该是CLKIQ /2正确吗?

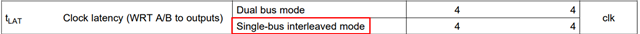

问题3. 如果 问题1是正确的,我认为解释"tlat"是很奇怪的。

因为,在交错模式下,当RESETIQ为高时,DAC不会锁定输入数据。 用于DAC的CLKIQ的CLK锁存器(实际上是CLKDACIQ)

因此,我认为在交错模式下,“WRT A/B”应该是“CLKIQ或CLKDACIQ”。 请您确认一下并提供您的反馈吗?

巴西,