主题中讨论的其他部件: AMC1304L25

为了获得来自ADC的数据,我们需要实施Sinc3过滤器。

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

//公司:

//工程师:

////

创建日期:15:37:12 2016年26月10日

//设计名称:

//模块名称:sinc3_Verilog

//项目名称:

//目标设备:

//工具版本:

//描述:

////

依赖项:

////

修订版:

//修订0.01 版://创建的文件

//附加注释:////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

模块dec256sinc24b

(

输入mclk1,/*用于clk filter */

输入重置,/*用于重置filter */

输入mdata1,/*要过滤的输入数据

*/

输出reg [15:0]数据,/*过滤输出

*/

输出reg data_en,

输入[15:0] dec_rate

);

/*在正凝边缘上读取数据*/

reg [36:0] ip_data1;

reg [36:0] acc1;

reg [36:0] acc2;

reg [36:0] acc3;

reg [36:0] acc3_d2;

REG [36:0] diff1;

reg [36:0] diff2;

reg [36:0] diff3;

reg [36:0] diff1_d;

reg [36:0] diff2_d;

reg [15:0] word_count;

reg word_clk;

reg enable;

/*执行sinc操作*/

always @(mdata1)

if (mdata1=0) ip_data1=0

<=37 'd

d0;/*将0更改为-1用于twos补码*/ else ip_data1 <=37 'd1;/*累 加器(R)以积分器的速度累加。

Z =一个样本延迟MCLKOUT =调制器

转换位速率*/

始终@(negedge mclk1,POSedge reset)

如果(重置)

开始/*

重置时初始化ACC寄存器

*/

ACC1 <= 37 'd 0;

ACC2 <= 37 'd 0;

ACC3 <= 37 'd 0;

否则

开始

/*执行累积过程*/

+ ACC1 <= ACC1

ACC2 <= ACC2 + ACC1;

ACC3 <= ACC3 + ACC2;

结束

/*抽取阶段(MCLKOUT/WORD_CLK)*/

始终@(POSedge mclk1,POSegge reset)

Begin

if (reset)

word_count <= 16;

否则

,如果(

word_count == dec_rate -1)

word + word 0;

End

Always @( POSedge mclk1, POSedge reset )

BEGIN

IF ( RESET )

WORD_clk <=1'b0;

ELSE

BEGIN

IF ( WORD_COUNT == dec_RATE/2-1 )

WORD_clk <= 1'b1;

ELSE IF ( WORD_dec_RATE -1)

WORD_clk <= 1'b0;

End

/*区分因素(包括小数

阶段)

以

较低的速度执行区分阶段(FIR)。

Z =一个样本延迟WORD_CLK =输出字

速率*/

始终@(POSedge word_clk,POSedge reset)

BEGIN

IF (RESET)

BEGIN

ACC3_D2 <= 37 'd 0;

diff1_d <= 37 diffd

37;diff2_d <= 37 'd 0;1 <= 37 'd 0;diff2 <='d 0;

diff3 <= 37 'd 0;

end

else

begin

diff1 <= ACC3 - ACC3_D2;

diff2 <= diff1 - diff1_d;

diff3 <= diff2 - diff2_d;

acc3_d2 <= acc3;

diff1_d <= diff1;

diff2_d <= diff2;

END

END

/*将sinc输出时钟转换为输出

寄存器

WORD_CLK =输出字速率*/

始终@( POSedge word_clk )

开始

大小写( dec_rate )16'd32:begin

data <=(diff3[15:0]== 16'h8000)? 16'hFFFF :{diff3[14:0], 1'b0};

end

16'd 64: begin

data <=(diff3[18:2]== 17'h1万)? 16'hFFFF : diff3[17:2];

end

128'd 16:begin

data <=(df53[21:5]== 17'h1万)? 16'hFFFF : diff3[20:5];

end

16'd 256:begin

data <=(ddiff3[24:8]== 17'h1万). 16'hFFFF : diff3[23:8];

end

16'd:begin

data <=(diff3[27:11]== 17'h1万)? 16'hFFFF : diff3[26:11];

end

16'd:begin

data <=(diff3[30:14]== 17'h1万)? 16'hFFFF:diff3[29:14];

end

16'd:begin

data <=(df53[33:17]== 17'h1万)? 16'hFFFF : diff3[32:17];

end

16'd:begin

data <=(df53[36:20]== 17'h1万)? 16'hFFFF : diff3[35:20];

END

DEFAULT:BEGIN

DATA <=(diff3[24:8]== 17'h1万)? 16'hFFFF : diff3[23:8];

终端

机箱

结束

/*同步数据输出*/

始终@( POSedge mclk1, POSedge reset )

BEGIN

IF ( reset )

BEGIN

DATA_EN <=1'b0;

启用<= 1'b1;

END

ELSE

BEGIN IF

((word_count = dec_RATE/2-1)&&B1'en;

<= b0;

END

ELSE IF ((word_count == dec_rate -1)&&~enable )

BEGIN

DATA_en <= 1'b0;

enable <= 1'b1;

end

else

data_en <= 1'b0;

end

end

end endmodule

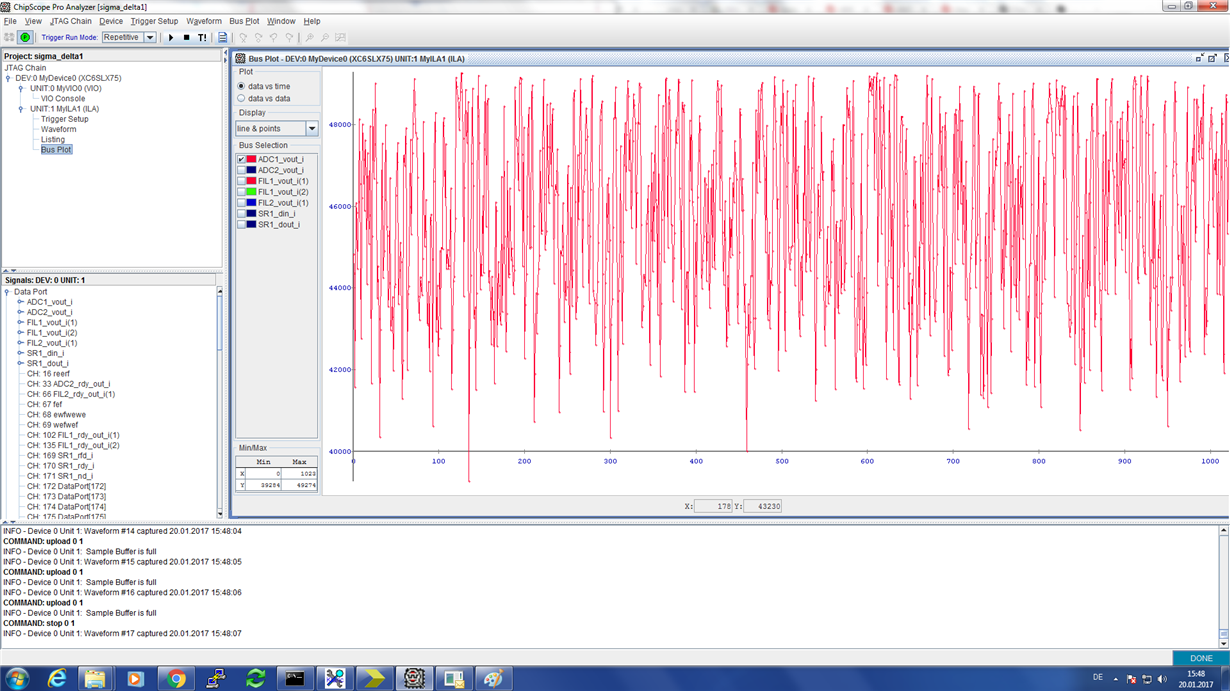

在实施过滤器后,我们应该会看到一个带有一些噪音的信号。 我们只会听到任何输入信号的噪音。 FPGA中是否有要实施的示例代码?