您好,

我正在脉冲调制模式下使用SMA100A信号发生器运行测试。 我有一个微型电路分离器,它将SIG gens输出分成ADC32RF45EVM的通道A和通道B。

我使用具有以下参数的旧GUI (ADC32RFxxEVM_revD_GUI)设置ADC和LMK时钟芯片

- FS = 2949.12MSps

- DDC设置为4X十进制IQ

- DDC频率设置为0

信号发生器设置为:

- 20MHz脉冲调制0dBm

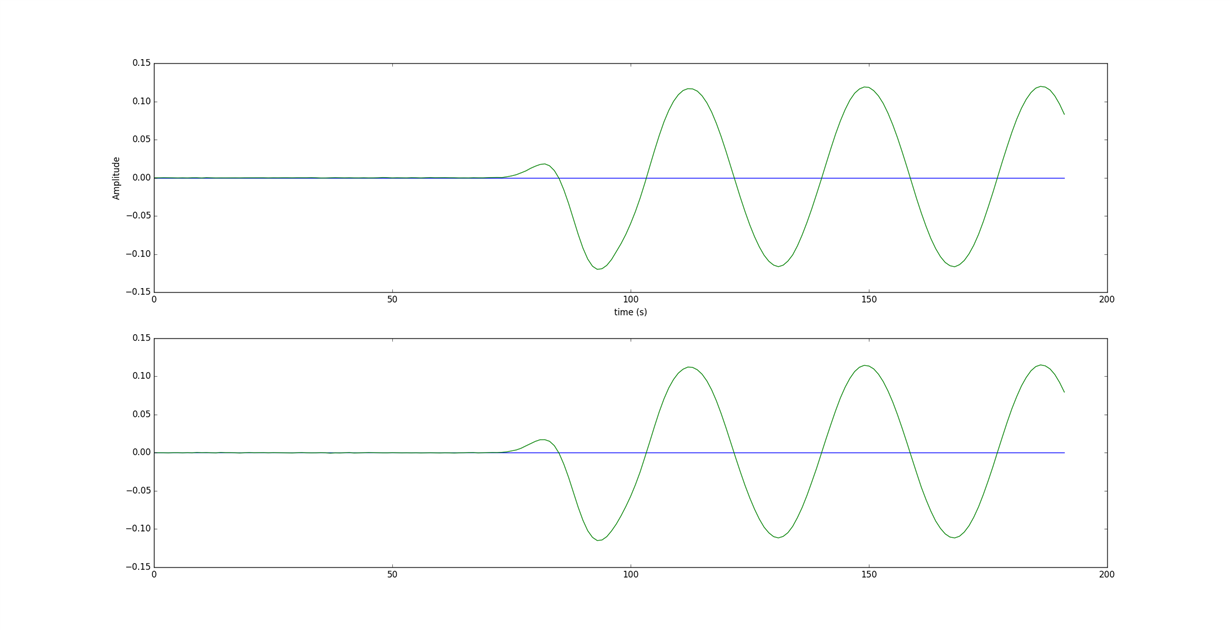

然后,我捕获并绘制一组样本。 如下所示。

第一个图是第一个ADC通道的IQ,第二个图是第二个ADC通道的IQ。 [免责声明:时标以示例表示,而不是以秒表示。 我忘记更改标题]

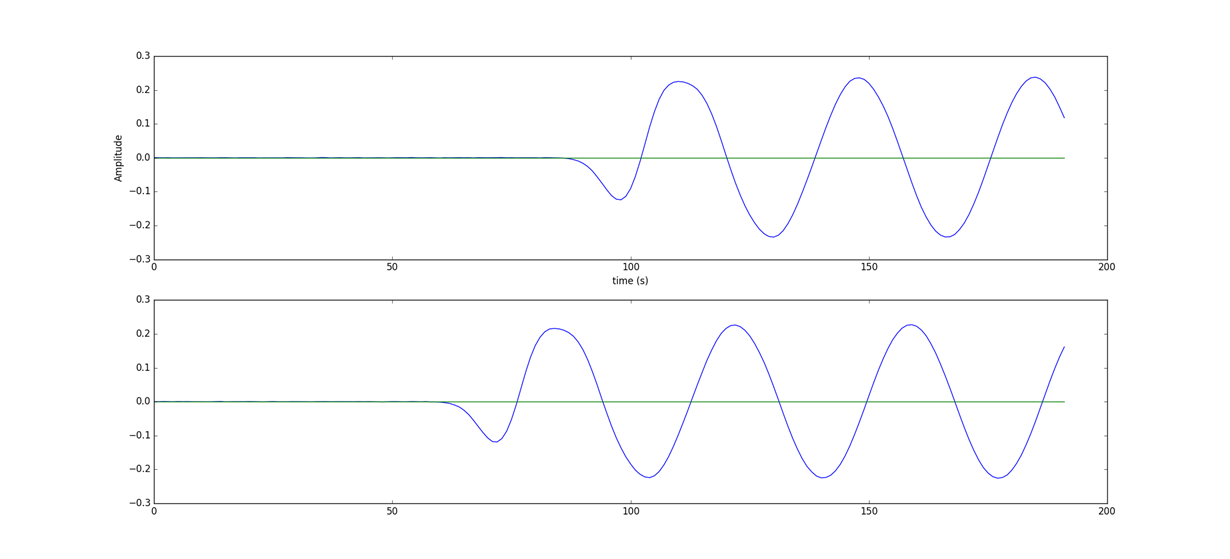

我使用新的GUI (ADC32RFxx EVM GUI)重复完全相同的测试,以设置ADC和时钟。

在这种情况下,图解(如下所示)包含通道A和B之间的时间偏移

如果您对此有任何反馈或想法,我将不胜感激。

此致,

马修·布里奇