Other Parts Discussed in Thread: ADS7955

大家好,

您是否可以帮助检查以下有关ADS7955 SPI的td2的问题?

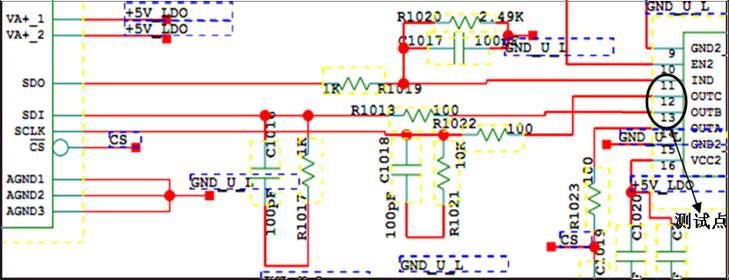

我的客户的主板上有td2=33.2ns,这比5V电源的最大td2(17ns)要高得多,SCLK=1MHz,SDO连接50pF负载。

他们还得到td3=14.75ns,比数据表中的MAX值高。

您能否帮助检查ADS7955数据表中td2和td3的测试条件? 时钟频率是多少,并在哪一点上进行测试(靠近主或从)?

如果这两种时间安排不能满足数据表的要求,是否存在任何风险? 解决方案是什么?

此致,

尼克·戴