请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:AFE5851 您好,

我使用的是Xilinx (Kintex 7) FPGA的AFE5851。 ADC的时钟频率为62.5 MHz,因此帧时钟频率为31.25 MHz。 反序列化由IDELAYE2和ISERDESE2基元在12位模式下实现。

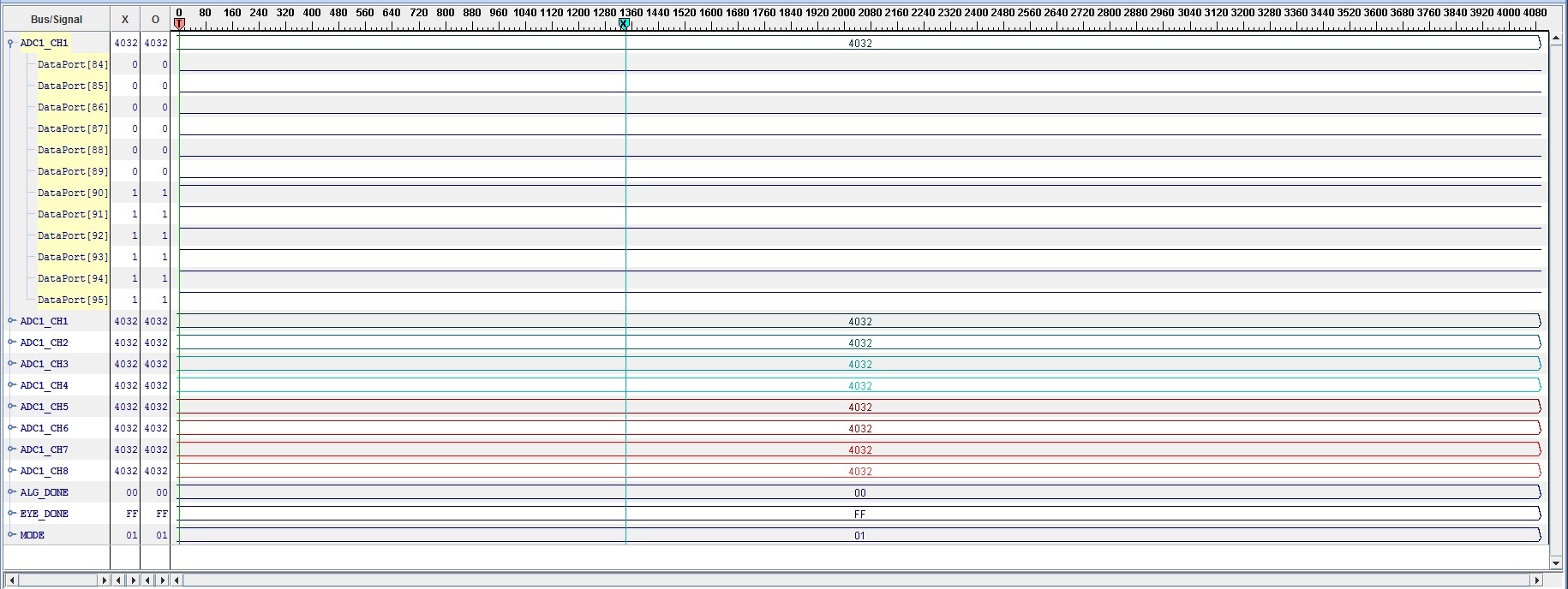

我使用校直模式来调整AFE5851的8个串行数据通道。 如下图所示,这种方法工作正常:

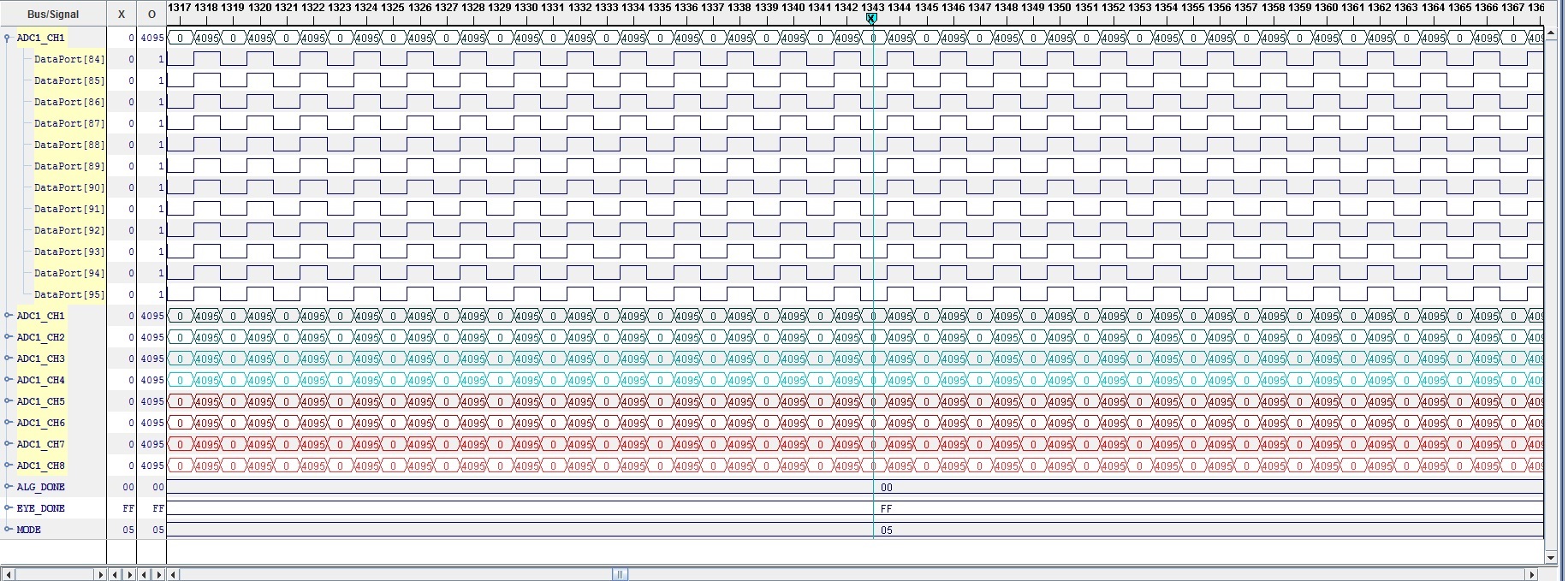

之后,使用同步模式对齐12位数据字。 这也很好:

要再次检查单词对齐,将选择切换图案,并按预期显示:

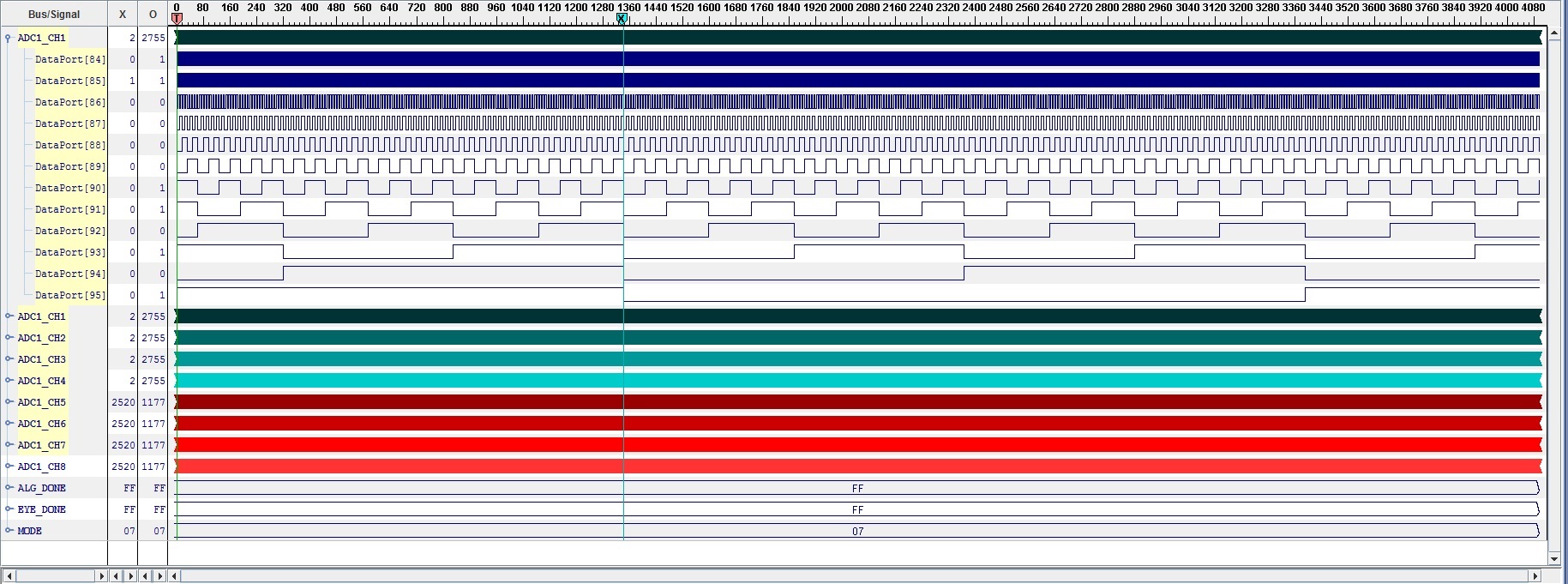

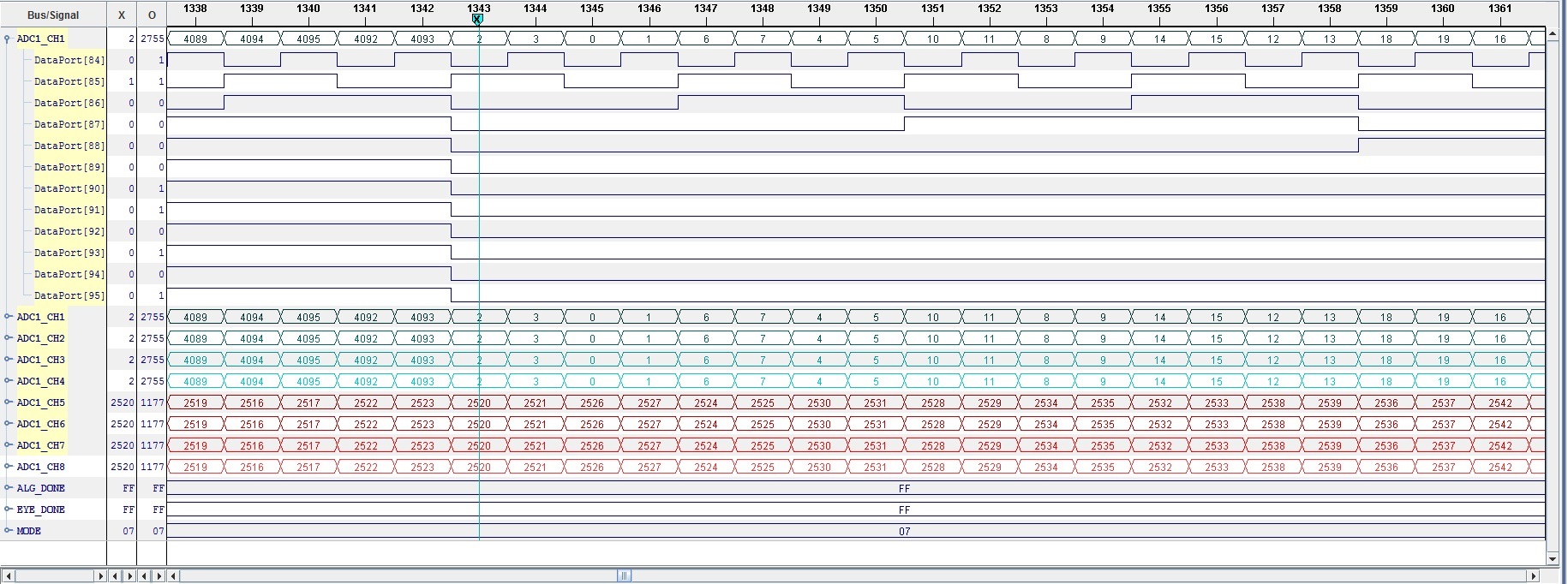

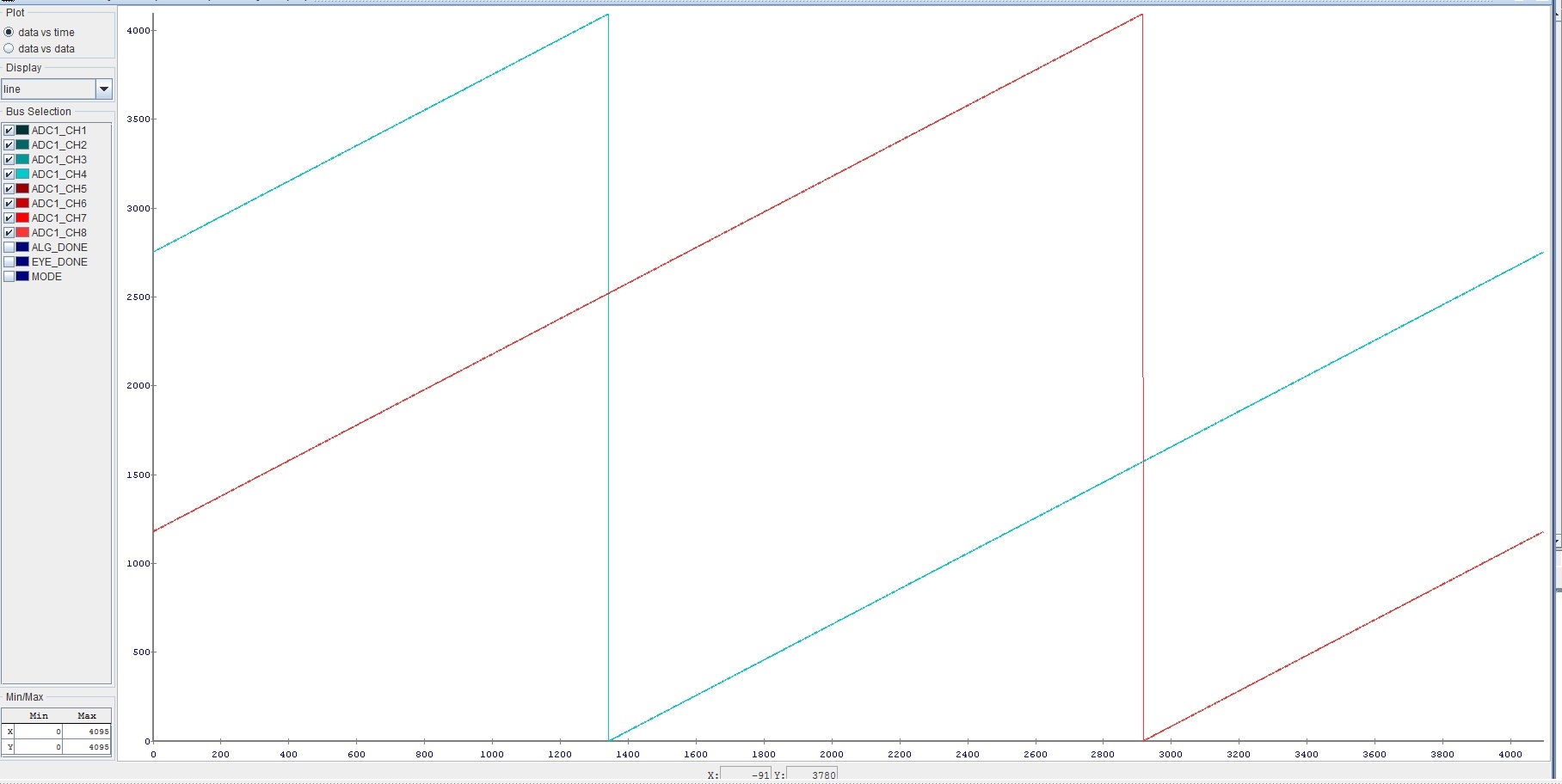

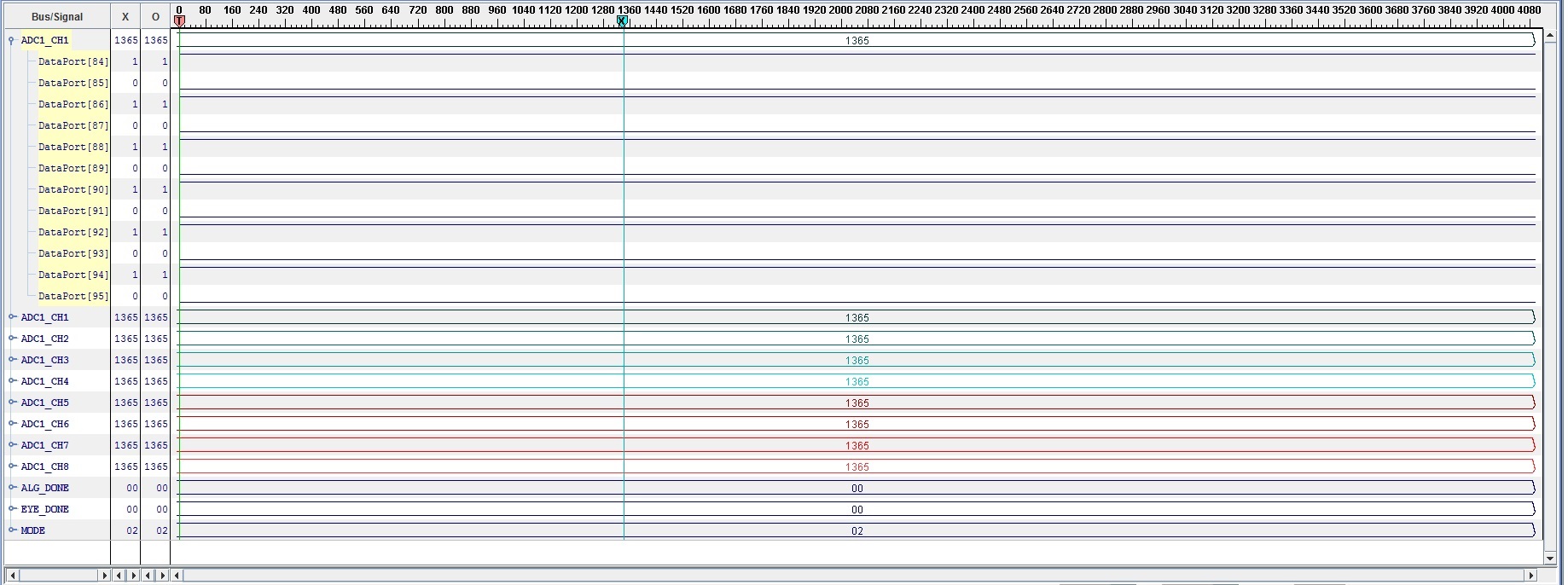

毕竟,坡道模式已激活。 乍一看,可以看到一个斜坡,但我正在处理两个问题:

首先,反序列化的位“dataport[85]”(它是ADC数据ADC1_CH1[11:0]中的位1)错误。 我不知道它是反向的还是延迟的。

其次,所有通道的斜坡模式都不是相位的。 通道1至4对齐,通道5至8 也对齐,但具有不同的相位。

因此,我的问题是:

1. AFE5851是否可能生成了不正确的斜坡模式?

2.为什么斜面图案未对齐,是否正确?

3.您认为我在FPGA接收器逻辑方面存在一般问题吗? 如何确定 问题是来自AFE5851还是FPGA逻辑,因为除斜坡之外的所有模式都正确反序列化。

此致,

菲利普