Other Parts Discussed in Thread: ADS9110, OPA625, OPA378, THS4551

主题中讨论的其他部件:REF5045, OPA625, OPA378, THS4551

大家好,我在一个电路板上使用24个ADS9110 ADC,并想为所有器件提供通用的4.5V参考(如果不是12个器件的参考)。 我计划遵循数据表中提供的基于REF5045和OPA625的设计,并为每个ADC提供3个10 UF电容器。 该设计将在2MHz采样时使用 ,我仍然希望在1LSB (3.8ppm x 4.5V = 17uV)内实现性能。

请您告诉我,数据表中提供的参考电路是否可以在此安排上重新工作?

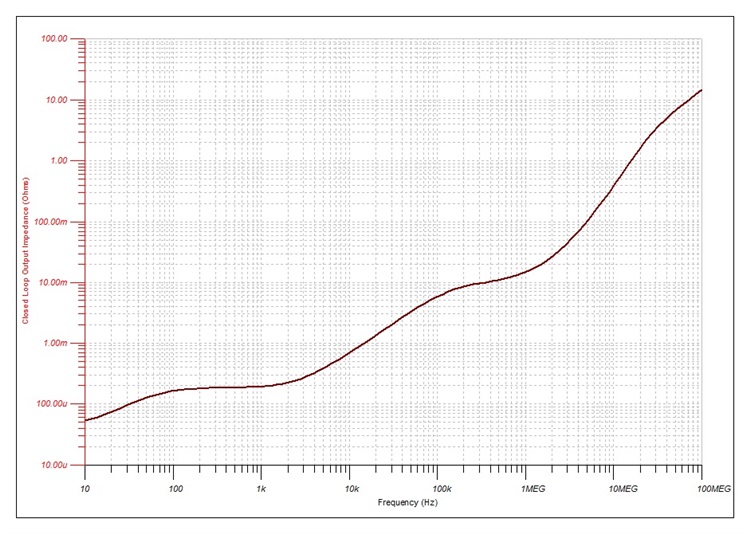

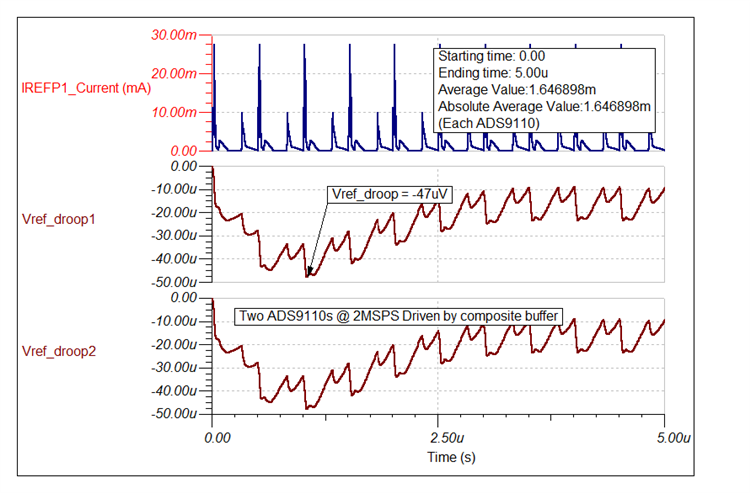

我使用了TINA并模拟 了具有360uF电容负载的参考电路(REF5045+OPA378+OPA625)。 我使用了15mA @ 2MHz的ILOAD, 波纹大约为21uV (近似值)。 此15mA @ 2MHz是否为用于测试电路的坡道? 这是2MHz表示的转换(即,在绘制Iref时的速率)吗?

我正在最后确定原理图,无法对此做出决定。 设计用于提供最佳SNR和动态范围。

我还希望在同一参考IC REF5045上连接一个单独的缓冲器,以便为24组THS4551全差动放大器生成VOCM (2.25V)。 是否允许这样做,或者我是否应该实施单独的电路以避免可能出现的故障?

我把模拟的TINA电路包括在内。

谢谢

此致

比利