Other Parts Discussed in Thread: DAC5672

大家好,

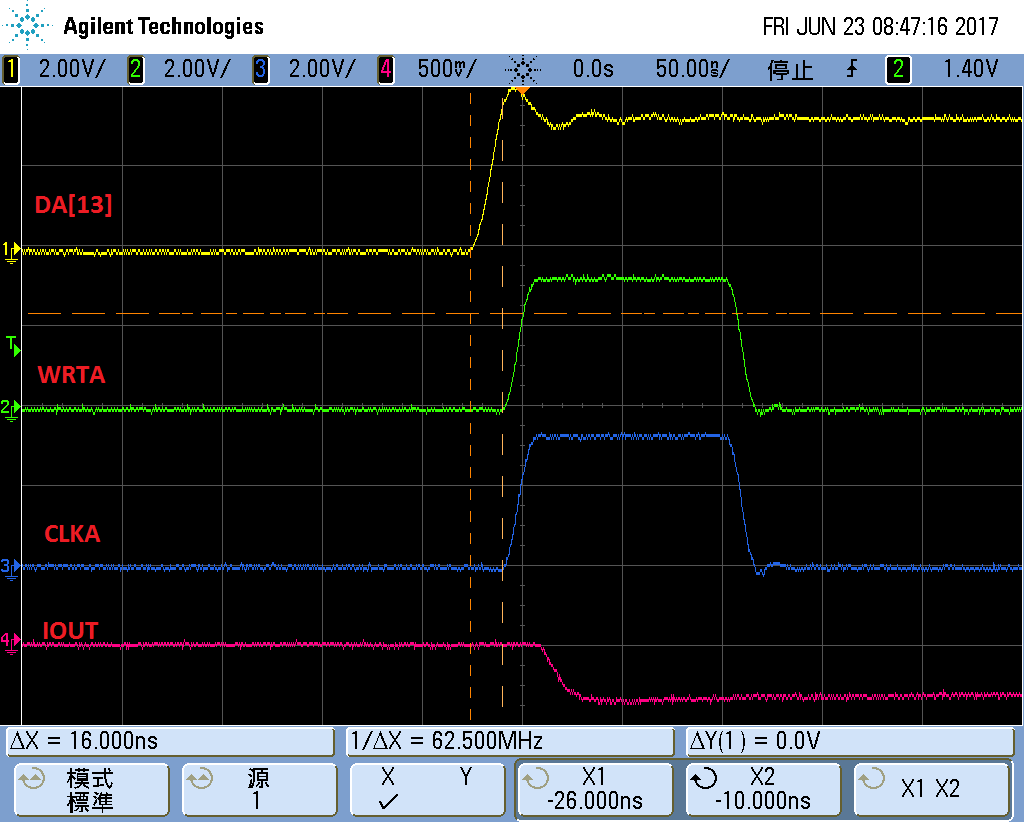

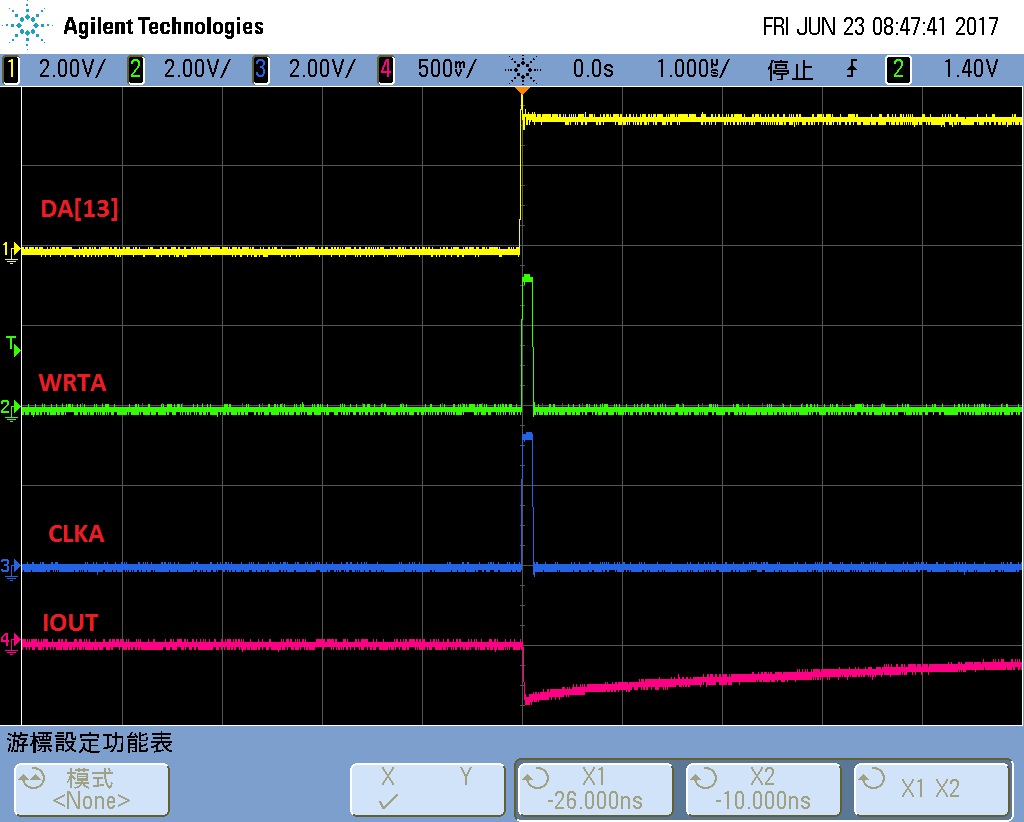

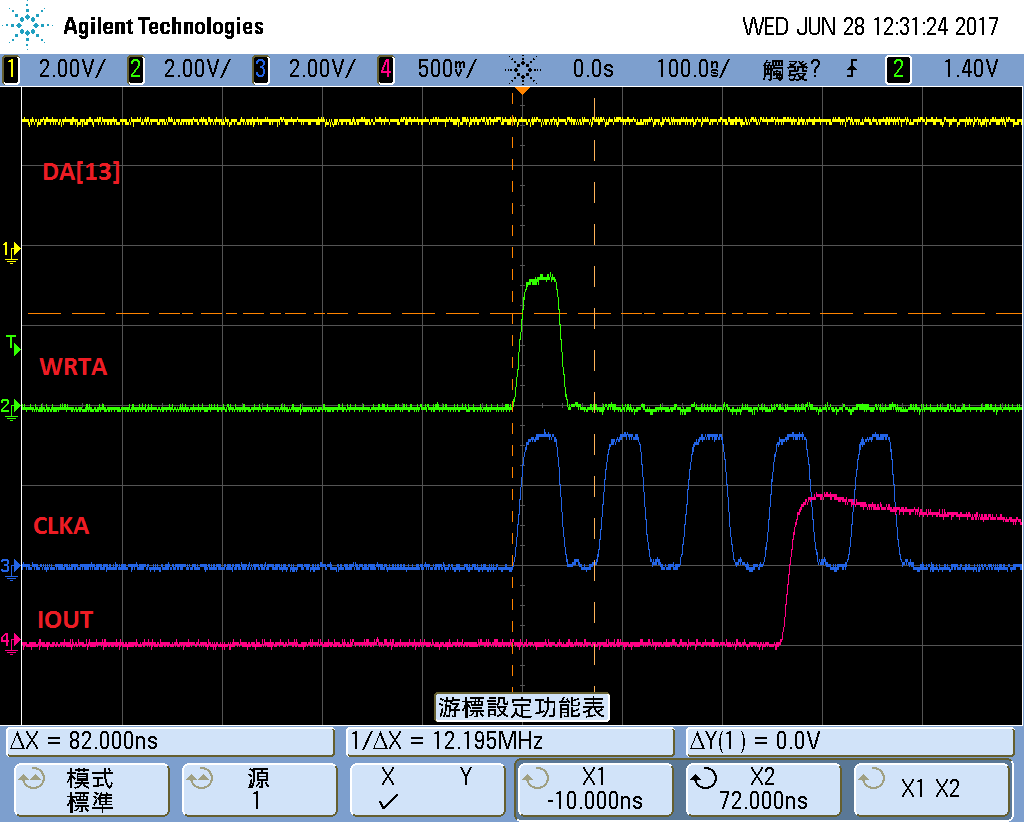

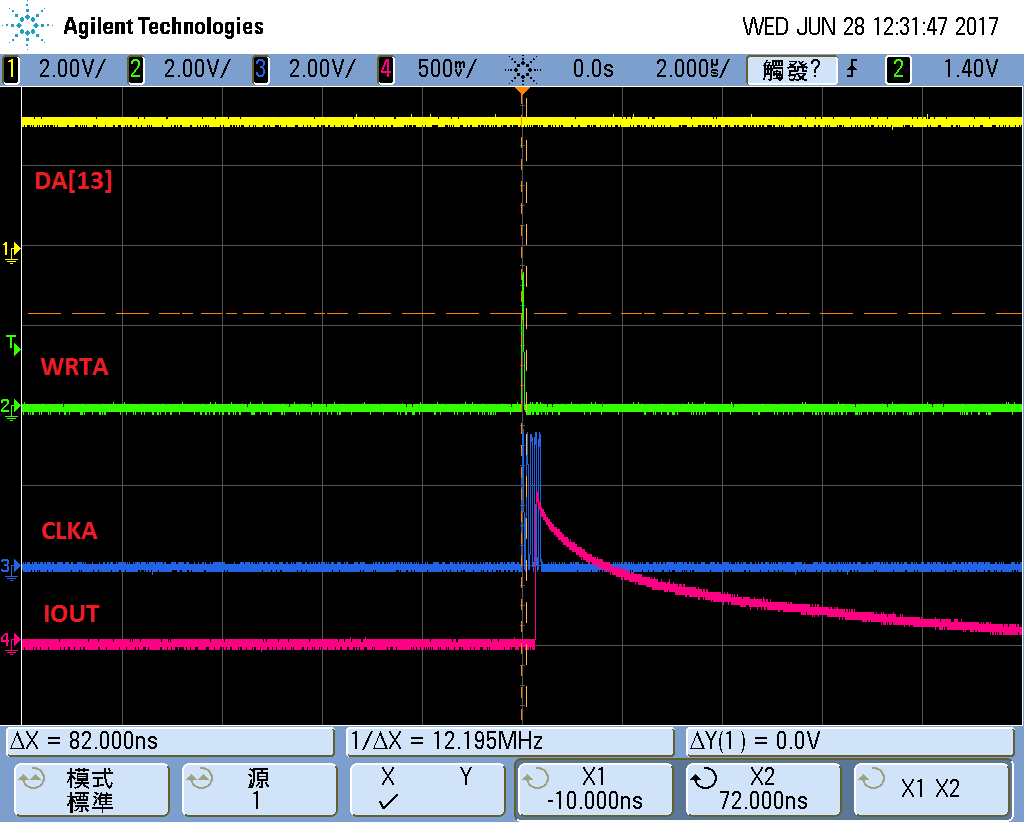

客户尝试使用其MCU控制我们的DAC5672 EVM,但它不起作用。 波形捕获连接在底部。

因为这是我们的EVM,所以我认为这纯粹是软件问题。

这是设置,请告诉我与设备通话的正确步骤,谢谢!!

模式=高,双总线

睡眠=低,操作模式

CLKA,CLKB,WRTA,WRTB在100ns时与相同的时钟脉冲同步

1.客户询问tLAT时钟延迟(WRTA/B至输出)最小值为4 clk,我们是否需要为CLKA,CLKB,WRTA和WRTB持续提供4 clk脉冲?

2.如果CLKA,CLKB,WRTA,WRTB仅需要一个时钟脉冲来更新DAC,在IOUT更新之前缺少哪些步骤?

非常感谢!!

Andrew