请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:DAC5689 尊敬的技术支持团队:

我对DAC5689有一些疑问。

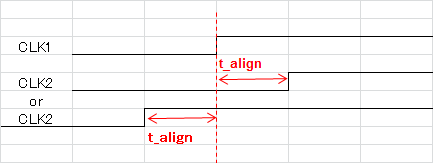

1) 对以下t_align的理解是否正确?

根据 数据表,我们使用fclk2=672Mhz和t_align is 190PS。

CLK1和CLK2之间的上升边缘关系应该超过±190PS,对吗?

CLK1=112MHz

CLK2=672MHz

2)

数据表显示t_align的最小值。 最大值如何?

如果时钟发生 器在 CLK1和CLK2之间增加了大量延迟,然后又增加了相同的上升时间,我猜这不是好的情况。

3)

CLK1和CLK2之间的时钟关系在 DAC5689内部是否存在温度变化?

电流t_align为400PS,当温度为0℃时DAC输出良好。

但℃温度为40 ̊ C时,DAC输出会在某个频率上导致杂散。然后在正确的频率上出现主提示音。

此致,

TTD