Other Parts Discussed in Thread: DAC3164, DAC3154

主题中讨论的其他部件: DAC3154

您好,

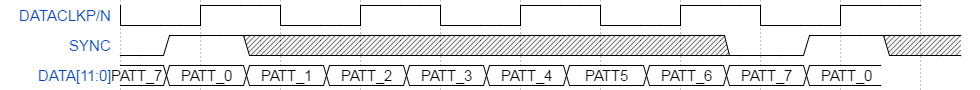

我正在尝试使用DAC3164的IO测试功能来验证FPGA的数字接口是否正常工作。 我阅读了此 线程,它提供了一些有关使用IO测试功能的信息,但我需要一些其他信息。

在双通道DDR模式中使用数字接口时,SIF寄存器中的iotest_pattern0-7字段如何用于IO测试? 与通道A和通道B相比,iotest_pattern0-7中的所有模式是否都是? 或者,有些模式仅与通道A进行比较,有些模式仅与通道B进行比较?

谢谢!

罗伊斯