主题中讨论的其他部件:CDCE7.201万,

您好,

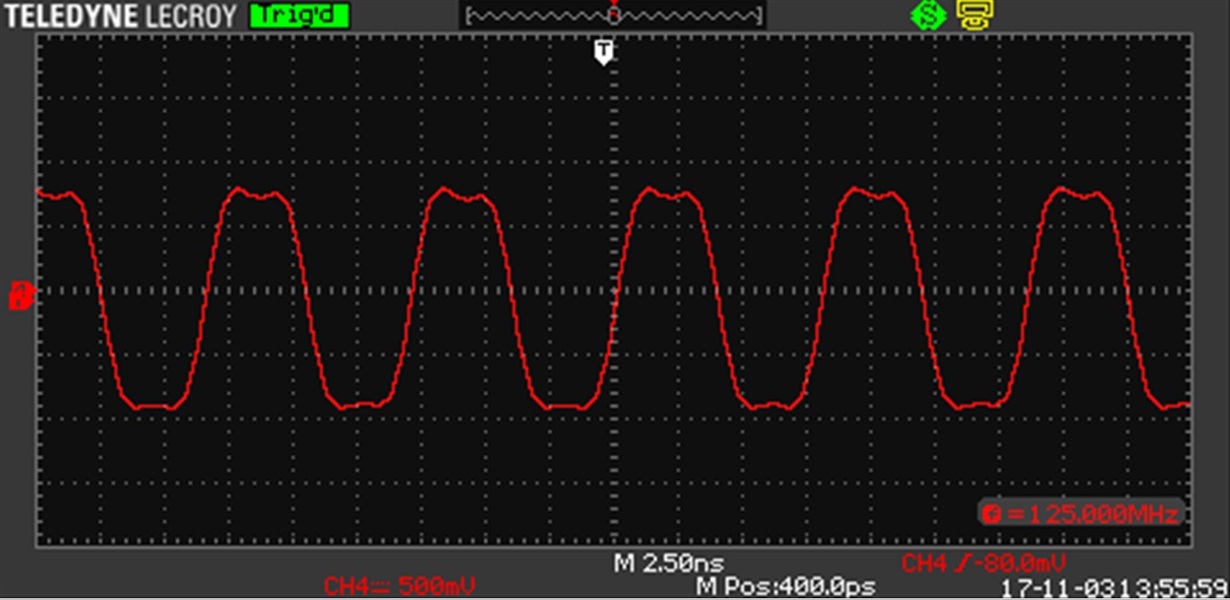

我们在FMC上有DAC5682Z DAC,它连接到Virtex 6 FPGA和CDCE7.201万,用于输入时钟。 几年来,我一直使用它来生成波形,没有任何问题。 但是当我尝试更高的采样率时,我得到了一些奇怪的结果。 我在500MSPS和1GSPS下进行了测试,我观察到以下内容:

|

主时钟(MHz) |

数据时钟(MHz) | 数据波形*(MHz) | DAC输出(MHz) | 预期DAC输出(MHz) |

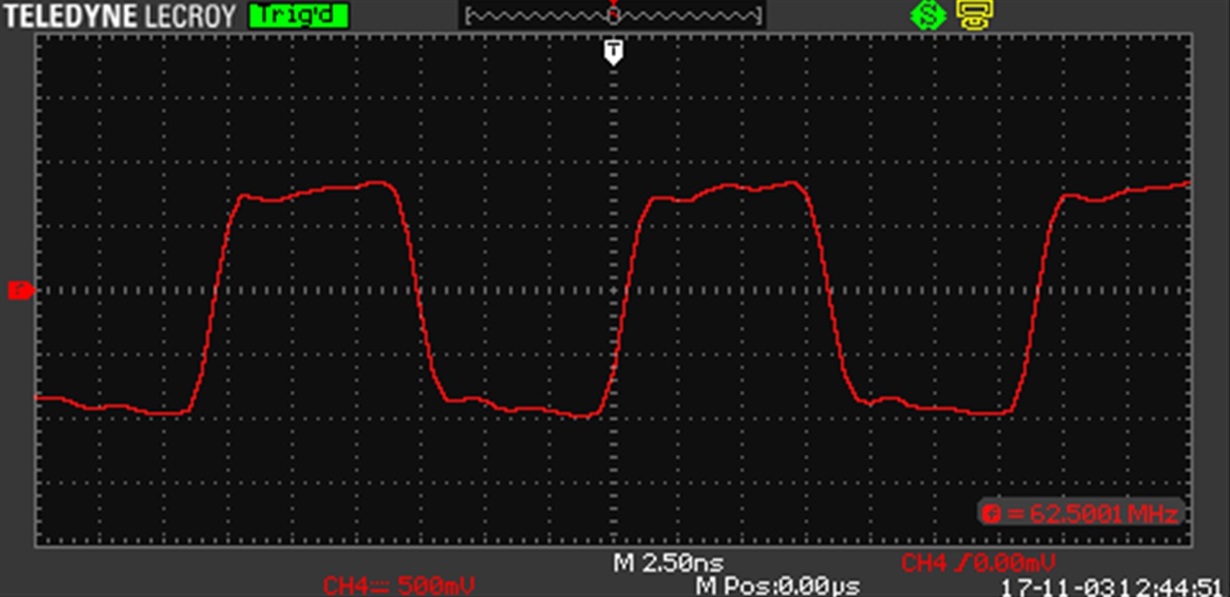

| 250 | 125. | 125. | 125. | 125. |

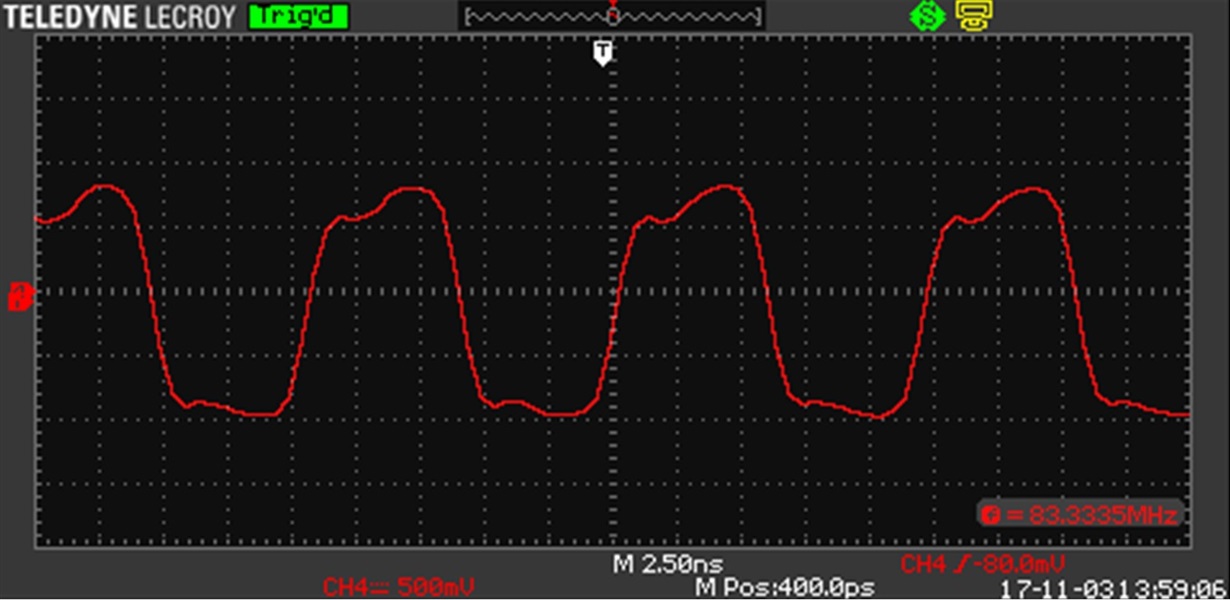

| 500 | 250 | 250 | 125. | 250 |

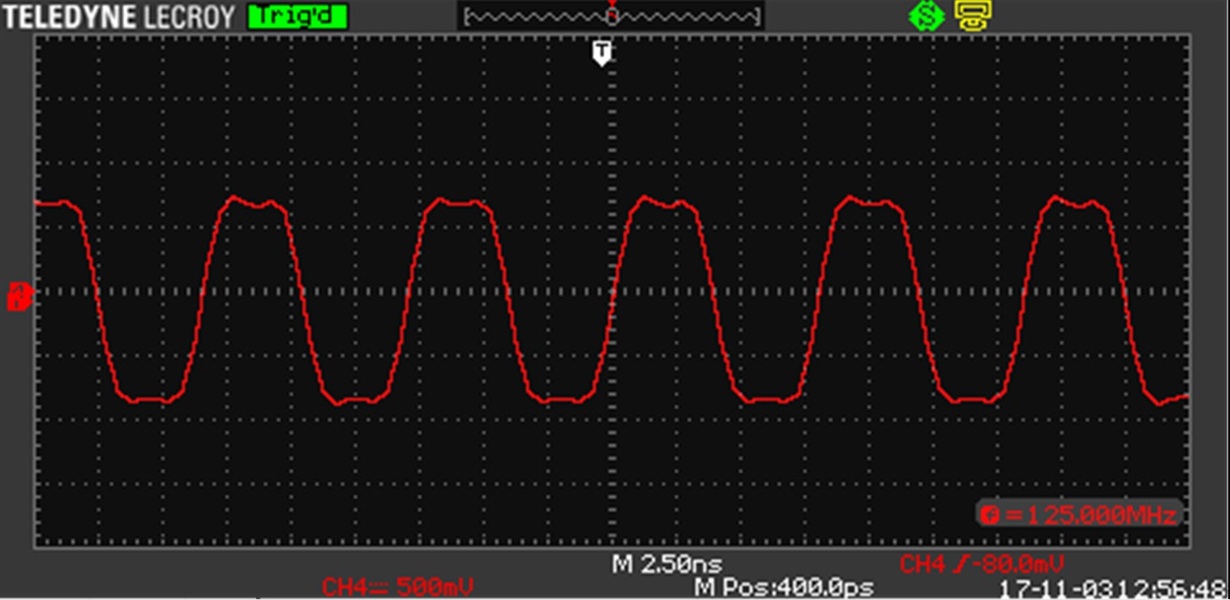

| 500 | 250 | 125. | 62.5 | 125. |

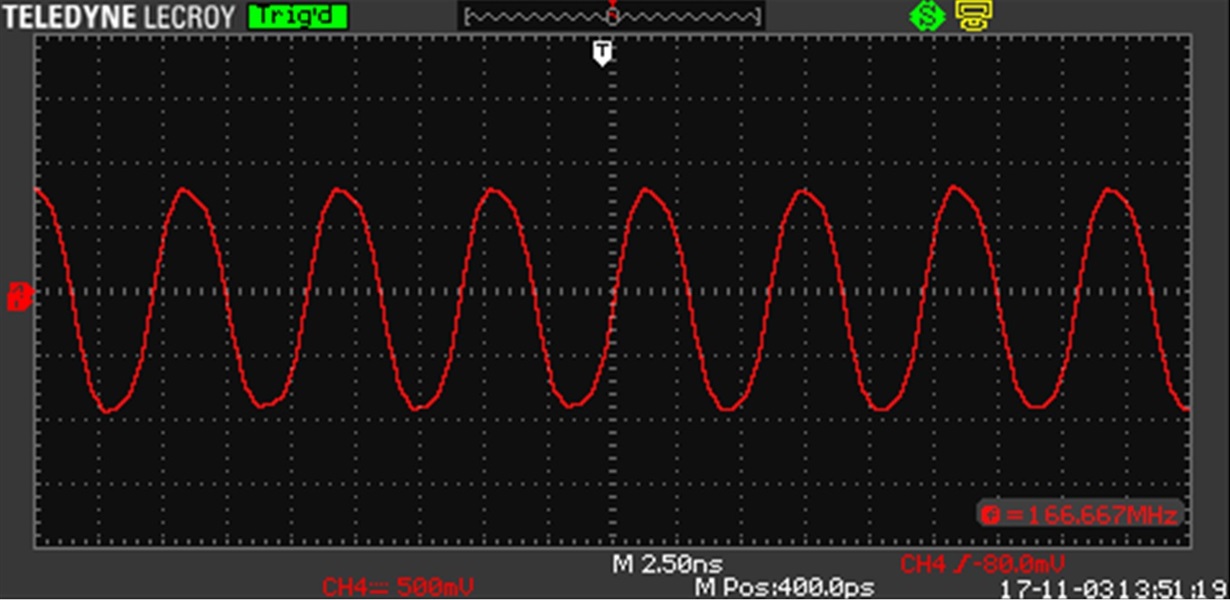

| 1000 | 500 | 500 | 166.667 | 500 |

*数据波形是交替的极端。

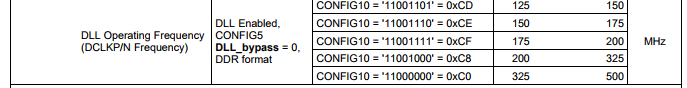

我已根据数据表中的表7.7 关闭了插值筛选器和PLL及AM设置DLL的配置10。 我还会在每125m个周期后发送相应的同步事件,

我想我错过了一些非常小的东西,这些东西导致了2和3这两个奇怪的因素,如果能帮助解决这个问题,我将不胜感激。

提前感谢。

此致,

Arpit。