主题中讨论的其他部件: TSW1400EVM

您好,

现在我正在使用 ADS5463EVM,并将LVDS输出连接到Xilinx Zynq SoC芯片。 我将所有LVDS输出转换为单端,并在Zynq器件内启用了终端电阻器。 我在没有和延迟的正边中读取ADC输出,但输出信号有很多故障。

1) 这些故障的原因是什么? 是否可能与阅读时间相关? 你有什么建议?

2)我知道ADC输出正在改变 干式的每一个边缘,哪一个是读取两个边缘上FPGA内部数据的最佳解决方案?

谢谢!

Amir

。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

现在我正在使用 ADS5463EVM,并将LVDS输出连接到Xilinx Zynq SoC芯片。 我将所有LVDS输出转换为单端,并在Zynq器件内启用了终端电阻器。 我在没有和延迟的正边中读取ADC输出,但输出信号有很多故障。

1) 这些故障的原因是什么? 是否可能与阅读时间相关? 你有什么建议?

2)我知道ADC输出正在改变 干式的每一个边缘,哪一个是读取两个边缘上FPGA内部数据的最佳解决方案?

谢谢!

Amir

。

埃米尔

有关如何使用两个时钟边缘的FPGA捕获数据的示例,请参阅随附的文档。

此致,

Jim

您好,Jim:

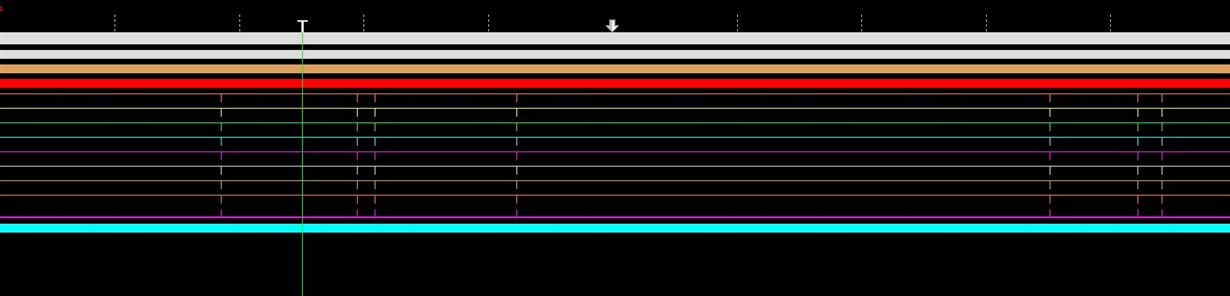

当我看到ADS 5463EVM的输出时,输出中有一些非连续波形。 实际上,我在Zynq芯片内使用了差分至单端缓冲器,将所有输出转换为 单端,然后将这些信号直接连接到Zynq SOC的输出引脚,因此我使用数字逻辑分析器捕获了输出, 它显示在没有输入时存在一些间断。下图显示了无ADC输入的输出(EVM板上的J11打开)

正如您所看到的,在一个时钟周期内,所有位同时都有相同的变化,较低的信号是干信号。 我不知道原因是什么,你怎么看?

Jim,

根据以下链接,TI在 TSW1200捕获卡上使用Xilinx FPGA,您的大学 Richard P已将此代码发送给您的客户。

请检查此页面。

谢谢!

e2e.ti.com/.../TSW1200-Source-Serial-v1p5.zipe2e.ti.com/.../TSW1200-Source-Parallel-DDR-ver1p6.zipAmir,1200,

固件通常与Verilog或VHDL源代码关联。 我附上了我能找到的内容。 希望这有所帮助。

此致,

Jim