Other Parts Discussed in Thread: ADS8028

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:ADS8028 专家,您好:

我的客户正在重复模式下使用ADS8028对模拟信号进行采样。

虽然我们发现如果在每个SPI周期之间将CS高时间设为几百ns的水平,ADC采样数据将显示错误,这意味着返回的ADC代码与模拟信号不能很好地匹配。

如果我们将每个SPI周期之间的CS运行时间从几个ns的hundereds增加到几个Us,我们就不会看到返回此ADC错误代码。

根据我们的数据表,最小CS高时间为6ns,如下所示

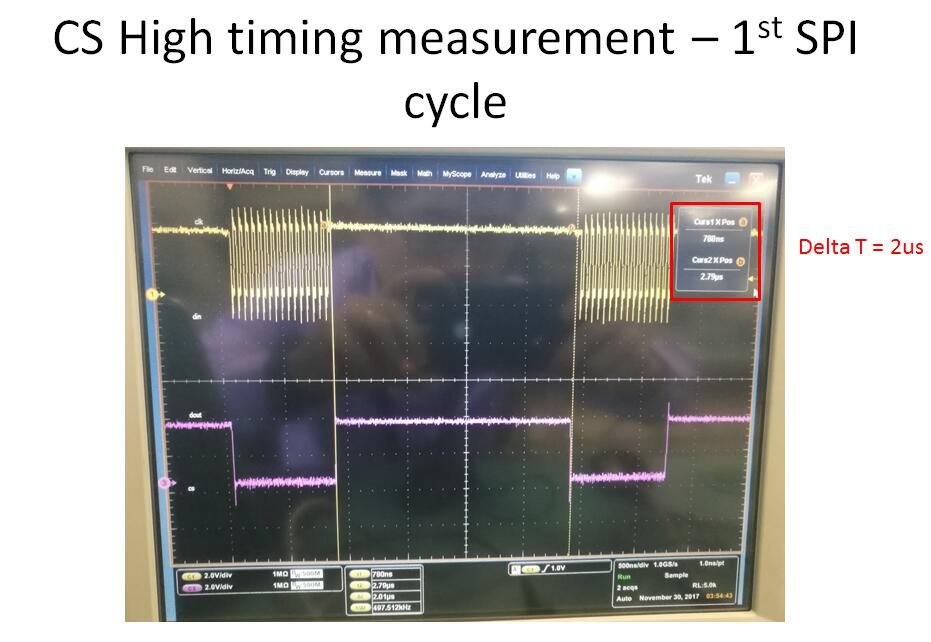

在重复模式下,我对TI EVM上的SPI计时进行了测量:

整体定时包括:第一个SPI周期写入控制寄存器,第二 个SPI周期等待转换完成,第三个SPI周期和随后的周期连续读回重建的ADC代码,如下所示:

第一个SPI周期和第二个SPI周期之间的CS高时间为2us,如下所示:

第二个SPI周期和第三个SPI周期之间的CS高时间很长,~26us如下所示:

以下SPI周期之间的CS高时间约为150ns:

我是否可以再次与您确认重复模式下每个SPI周期之间的CS高时间是否有任何特殊要求?

感谢您的提前帮助!

纱线