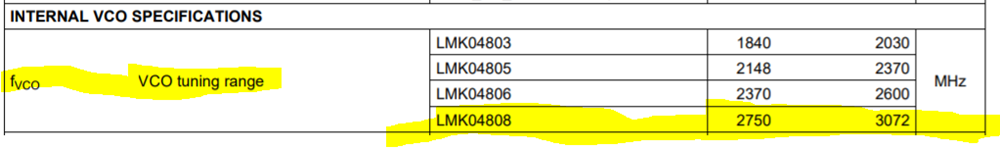

主题中讨论的其他部件: TSW1400EVM, DAC34SH84, LMK0.4808万

您好,

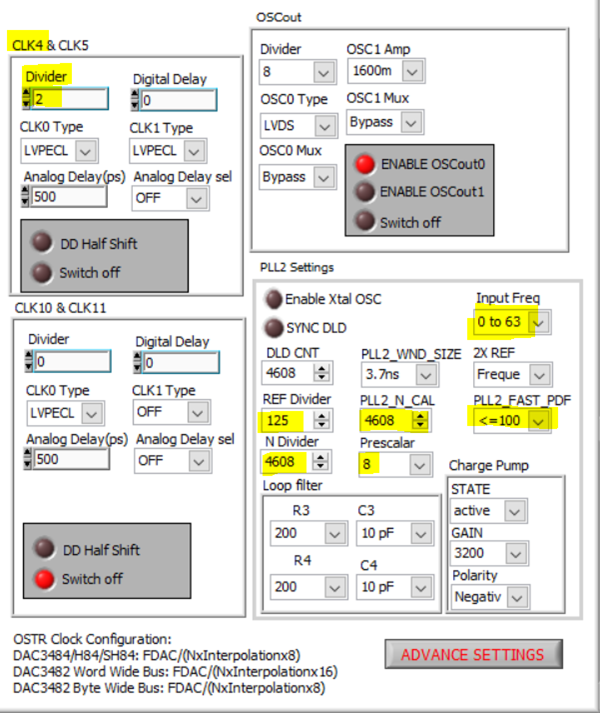

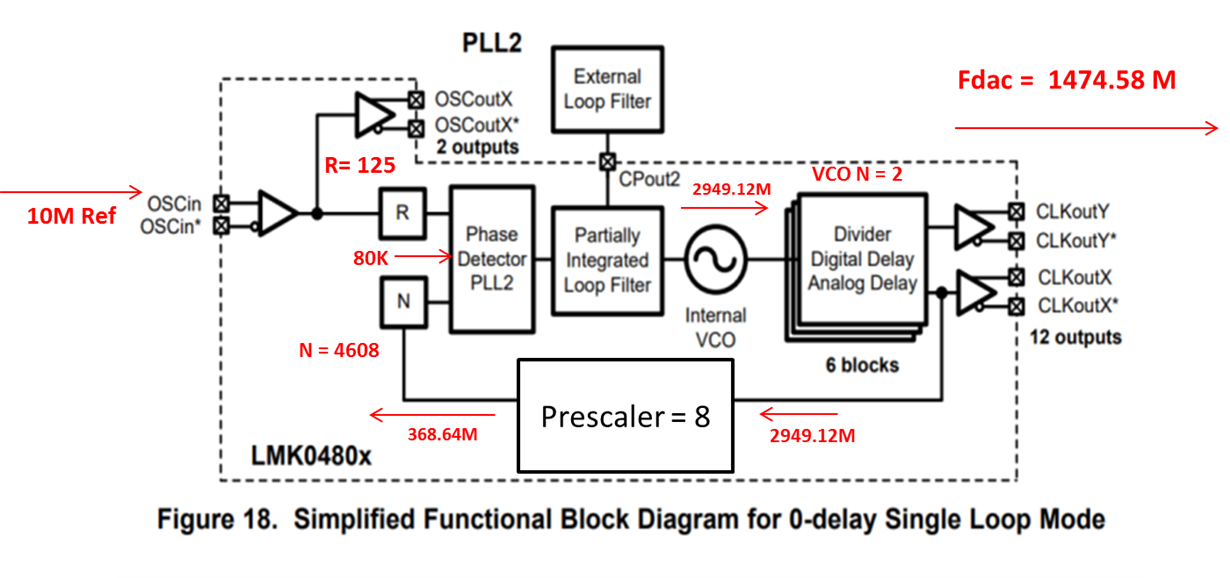

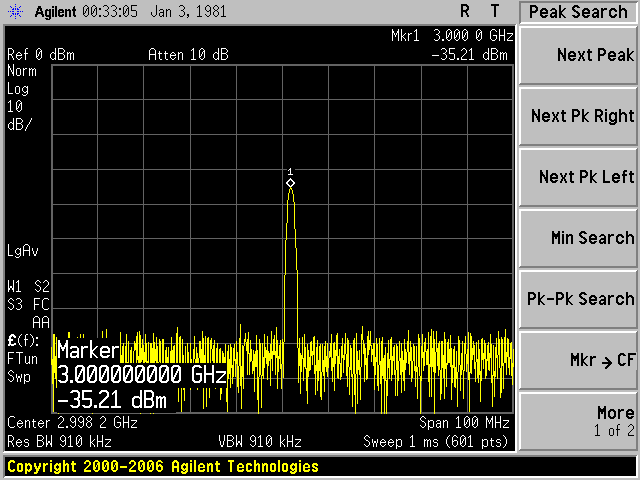

我目前正在尝试使用TSW30SH84EVM上的PLL设置来控制DAC时钟频率,并且在参考手册中的示例中遇到了问题。 我想知道是否可以收到一些指导,以便在TSW308x GUI中使用此设置来控制高速数据转换器Pro中的DAC时钟频率和数据速率? 即使它只是一个使用PLL设置来设置DAC时钟频率的配置文件,也会非常有用。 我还想知道是否可以使用此PLL设置来设置我选择的任何数据速率,以便与TSW1400EVM配合使用?

谢谢!

Joshua Johnson