线程中讨论的其他部件: DS90LV001, LMK0.4828万, TSW14J56EVM

有关ADS42JB69的SYNC和SYSREF输入的快速问题。

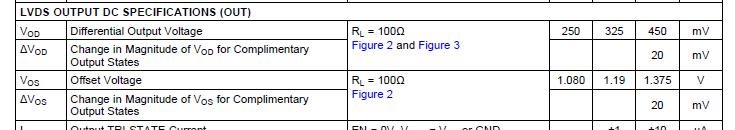

DS90LV001 LVDS缓冲器将用于从FPGA驱动这些信号,但我们希望确认接口的兼容性。 以下是DS90的LVDS驱动器规格:

尽管AD42JB69仅提供典型的LVDS电平(Hi =1.3V,Lo =0.5V,VCM =0.9V),但我认为它可以接收DS90LV001缓冲器的LVDS差分信号范围。 这是否正确?

共模电压不一致:DS90为1.19V,ADS为0.9V。 我假设这意味着信号必须是交流耦合的。 请确认。