您好,Joachim和Joseph:

去年,我们一直在讨论使用ADS124S08的最新设计(https://e2e.ti.com/support/data_converters/precision_data_converters/f/73/p/60.2523万/2263474#pi318173=2)226.3474万)。31.8173万。

我发现了下面讨论的DOUT/DRDY输出电平的第一个问题的答案-当CS较高时,输出变为"Hi-Z"状态! 这在一些正时图上可能会被注意到,但我在ADC手册的文本中没有注意到它!

我在第二个问题上做了更多的工作,发现如果我先读取转换数据,然后更改测量输入,即写入IDACMUX和IMPMUX! 它看起来就像ADC在连续转换模式下的行为一样。 但是我已将模式设置为单影像!?

我的寄存器的值如下所示:

INPMUX = 0x12

PGA = 0x0C

datarate = 0x34

Ref = 0x92

IDACMAG = 0x80xF0240

SYS = 0x10

数据速率寄存器中的模式位设置为1-单次激发转换模式。 我希望在这种模式下,转换结束后,ADC处于待机状态/模式写入寄存器不会清除转换数据并触发新的转换!

请评论!

----------------------------------

现在,我的原型板已启动并运行,但有两个问题可能相关:

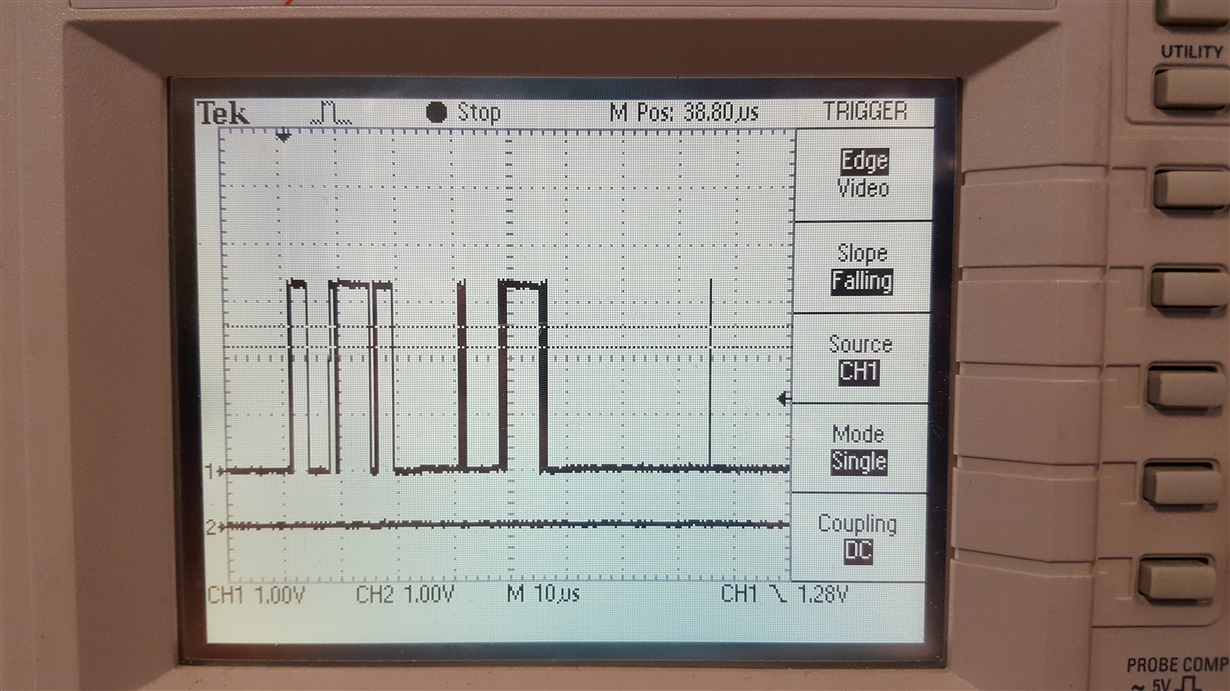

第一个问题是DOUT/DRDY输出中有奇怪的低信号电平! IO已附上示波器的图片,显示DOUT/DRDY,SCLK和DIN信号以进行比较。

CLK和DIN信号的“1”和“0”电平良好,但DOUT/DRDY在数据传输之间保持在大约2.2V的电平,在数据传输期间,“1”电平要么良好(3.3V),要么低(2.2V)。

PIC中的通信表示转换完成且DRDY降低后的序列:

1-写入IDACMUX,仅将IDAC1设置为下一个AINx (从不使用IDAC2)(写入3字节);

2-从同一寄存器读取(读取3字节);

3-写入IMPMUX以选择下一个输入AINx (写入3字节);

4-从同一寄存器读取(读取3个字节);

5–从上一次测量中读取转换数据(无状态或CRC)(读取3字节);

6–发送启动命令(0x08)以开始下一个转换(1字节写入)。

我不使用读取命令,只生成3x 8位时钟序列! 这是否正常?

请评论!

我的第二个问题是,我与ADC寄存器的所有通信似乎都是良好和正确的,即写入寄存器的值可以从寄存器中读取,并且是相同的。 但是,当我读取转换数据时,我总是得到0!

ADC原理图位于上述线程中,我们当时讨论过该线程。 使用的微控制器是LPC2368。 PT100可能与系统的第一个和第二个输入(腔室和样品输入)连接,也可能未连接,但这没有任何区别! 系统的第三个和第四个输入使用100欧姆和22欧姆的校准电阻器,因此它们应该给我两个不同的ADC转换值,模拟PT100温度探头的0°C和-180°C输出。

但是,我从所有4个测量通道中获得0值。 DOUT/DRDY上的低信号电平可能是导致这种情况的原因吗?

请评论!

此致,

尼古拉