大家好,

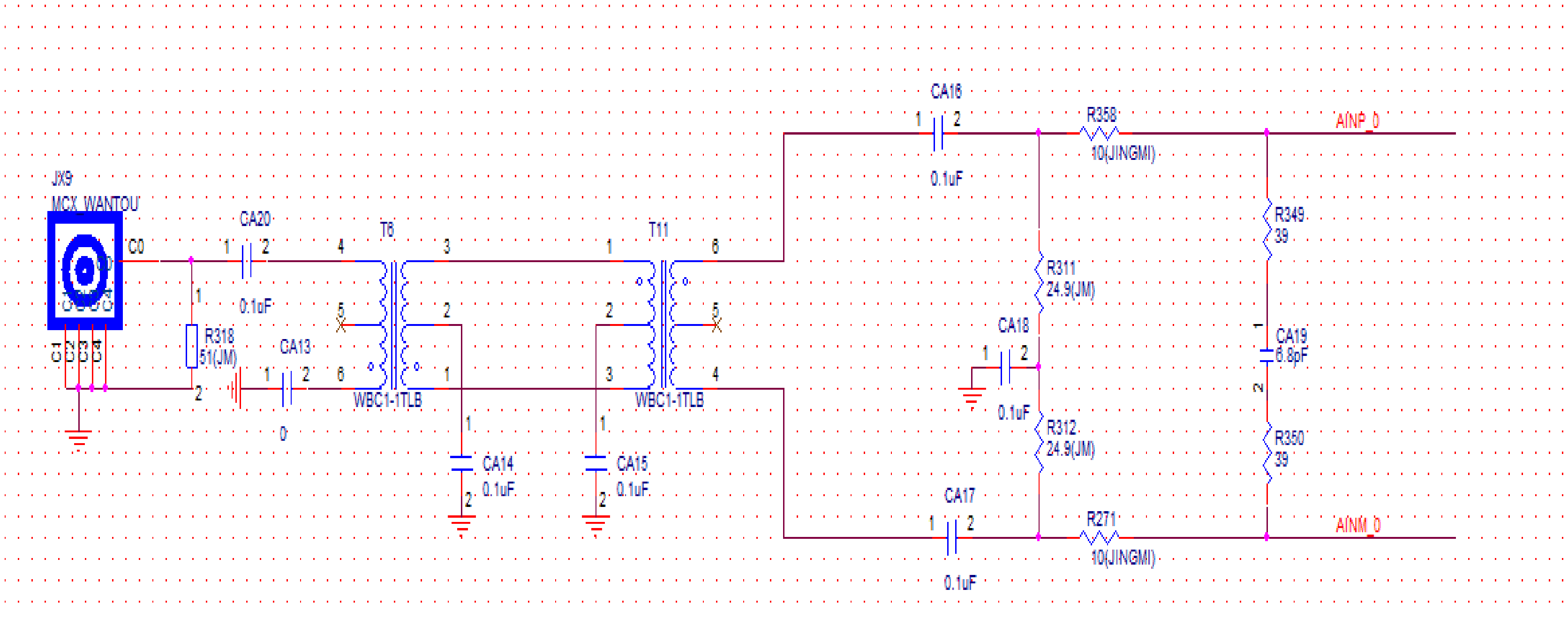

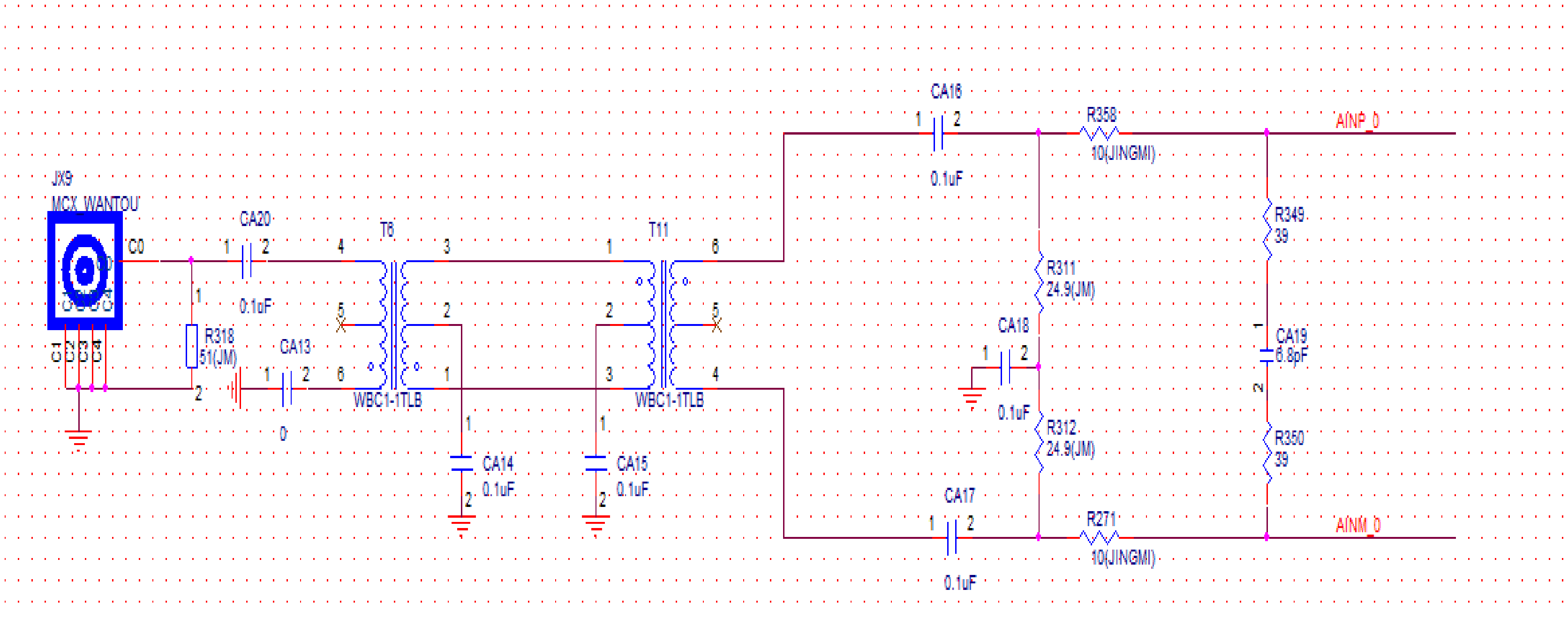

输入外部时钟采样率204.8M,输入信号0dBm,中心频率153.7M,信号外部添加带通滤波器,频谱基本正常, 正极非常小,基本符合器件的特性。 但是,当输入信号达到-22~-40dBm时, 信号两侧的正变大,不会随着信号输入振幅的减小而减小。 请参见下图中的黄色文本。 在几个不同的主板上发现了这个问题,现在的主要问题是为什么当信号输入振幅降低时,两侧的杂波增加。 我们怀疑这是ADC自身采样的问题。 信号源和时钟的问题可以消除。 第二个数字是我们的前端电路。

此致,

罗艾米

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好,

输入外部时钟采样率204.8M,输入信号0dBm,中心频率153.7M,信号外部添加带通滤波器,频谱基本正常, 正极非常小,基本符合器件的特性。 但是,当输入信号达到-22~-40dBm时, 信号两侧的正变大,不会随着信号输入振幅的减小而减小。 请参见下图中的黄色文本。 在几个不同的主板上发现了这个问题,现在的主要问题是为什么当信号输入振幅降低时,两侧的杂波增加。 我们怀疑这是ADC自身采样的问题。 信号源和时钟的问题可以消除。 第二个数字是我们的前端电路。

此致,

罗艾米

Amy,您好!

根据我们使用您的价值观进行的测试,您的spurs似乎是基础色调的奇序谐波。 我能够通过信号发生器设置在-22dBm的情况下识别HD3至HD19。这使我的基本音调大约在-35 dBFS (您的看起来接近-31 dBFS)。 我确实注意到,在较高幅度下,spurs较低,而在较低幅度下,spurs较低,通常在-70 dBFS (或-50 dBm输入)左右消失。

它们收集得如此接近的原因是输入信号频率(153.7 MHz)与时钟频率(204.8 MHz)的关系。 您的弦谐波几乎正从其他尼奎斯特区域折叠到您的基础上。 稍微调整频率将开始在更宽的频段上涂片谐波,这将使滤波器进一步降低谐波。

奇数谐波的水平接近-95 dBFS。 如果您参考数据表,则此值在该设备的预期性能范围内。 SNR为73.6 dBFS,对于170 MHz,其典型值为73.2 dBFS。 如上所述,正确的频率规划将允许您使用滤波器进一步降低这些谐波。

希望这有所帮助。

谢谢!

已绘制