主题中讨论的其他部件:ADC12DJ3200

当我使用Xilinx JESD内核时,我终于能够获得一个仿真工作,但是当我在硬件中尝试我的设计时,它不起作用。

一个可能的问题是ADC12J3200EVM具有4个反向JESD通道。 在示例项目(https://www.ti.com/technical-documents/mytilit/export-control?litId=SLVC698&fileType=zip&&ts=1650494201216)附带的FPGA版本上,有以下说明

ADC12DJ3200 revA EVM用于测试。 在此EVM中,上部四个SERDES通道的P & N修订版引脚被交换,因此在设计中实施了Rx通道极性反转以解决此问题。 因此,分配给PHY模块的Rx信道极性反转常量为240。

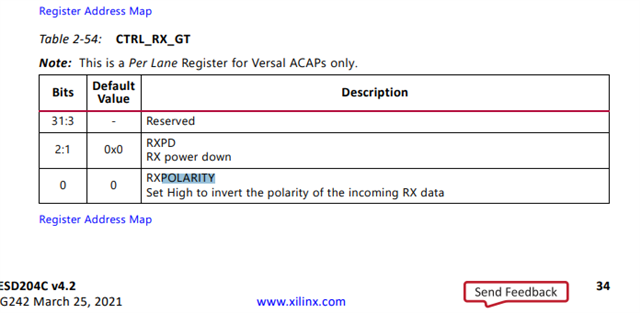

在Xilinx工具的2020.2 版本中,似乎JESDPHY的极性输入不再存在,我没有看到一个不是“Versal ACAP”的寄存器,它只有具有策略 性设置(下面是Xilinx docs.xilinx.com/.../pg242-jesd204c的JESD核心产品指南 )

所以我的问题是,如何使最后4个通道的极性引脚反转。